# PRODUCT OVERVIEW

# OVERVIEW

Samsung S3C380D 16/32-bit RISC microcontroller is a cost-effective and high-performance microcontroller solution for TV applications.

Among the outstanding features of the S3C380D is its CPU core, a 16/32-bit RISC processor (ARM7TDMI) designed by Advanced RISC Machines, Ltd. The ARM7TDMI core is a low-power, general-purpose microprocessor macro-cell that was developed for use in application-specific and customer-specific integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost-sensitive and power-sensitive applications.

The S3C380D was developed using the ARM7TDMI core, CMOS standard cell, and a data path compiler. Most of the on-chip function blocks were designed using an HDL synthesizer. The S3C380D has been fully verified in the Samsung ASIC test environment.

By providing a complete set of common system peripherals, the S3C380D minimizes overall system costs and eliminates the need to configure additional components.

The integrated on-chip functions that are described in this document include:

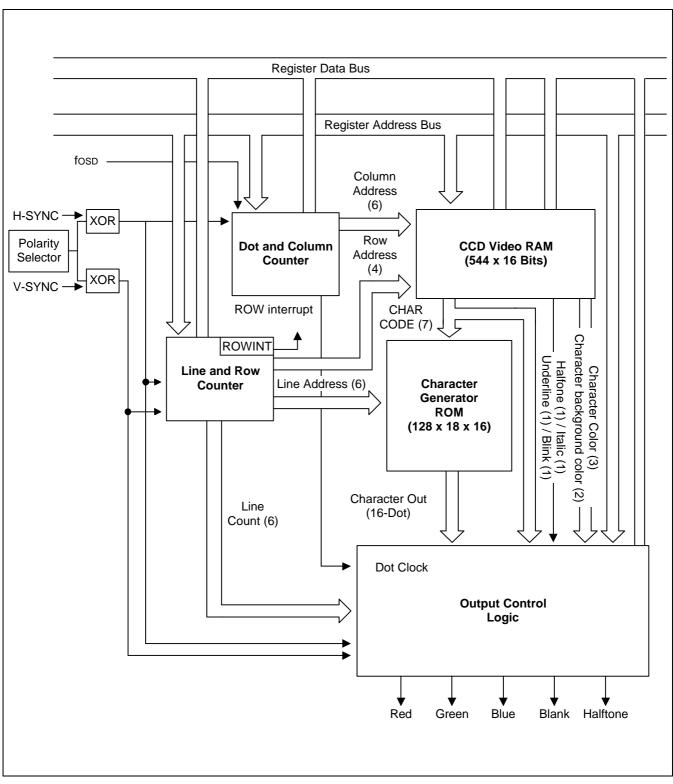

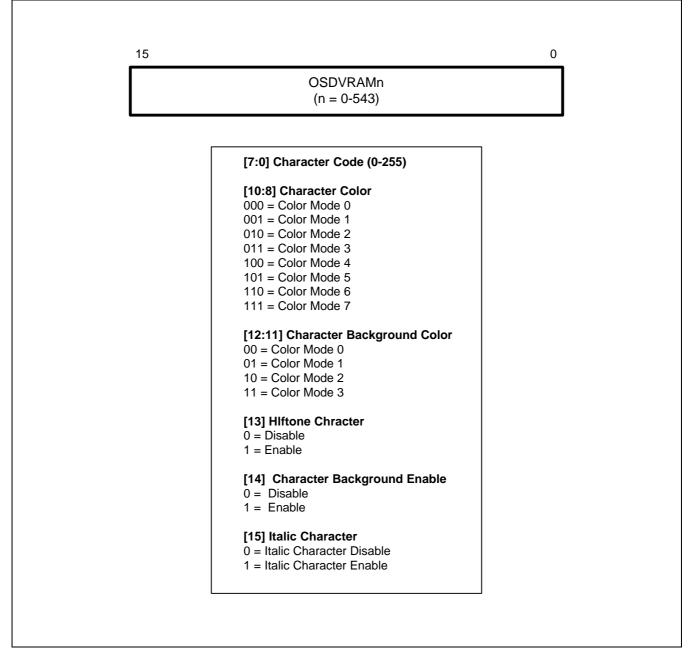

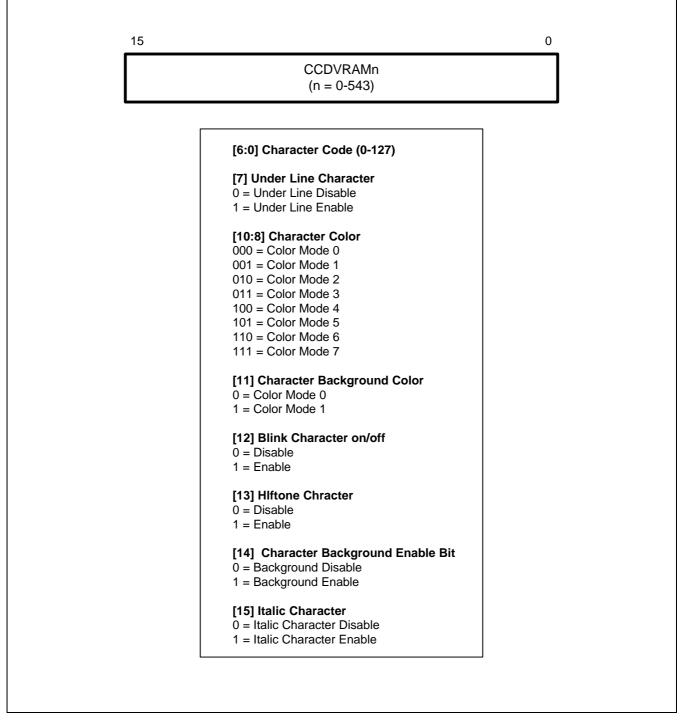

- 4-Kbyte RAM (3008-byte (1504 × 16 bits) general register and 1088-byte (544 × 16 bits) OSD/CCD RAM)

- 128-Kbyte internal program memory

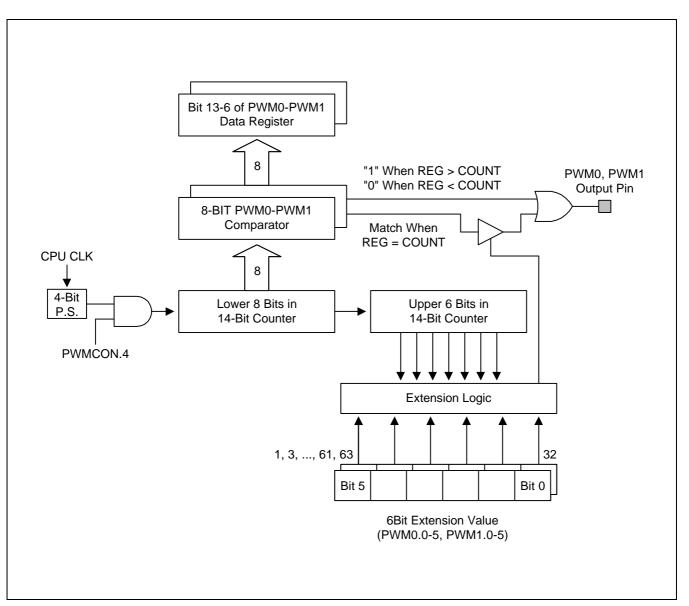

- Two 14-bit PWM modules

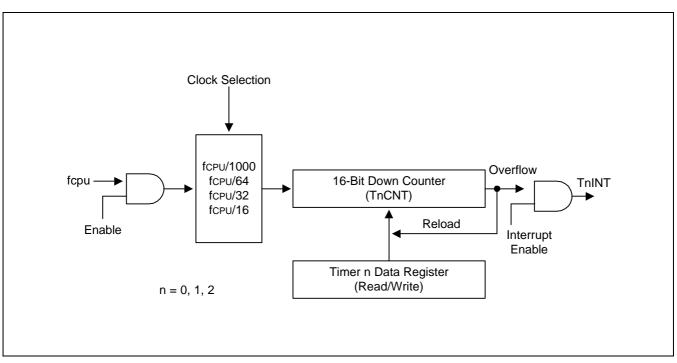

- Three 16-bit timers

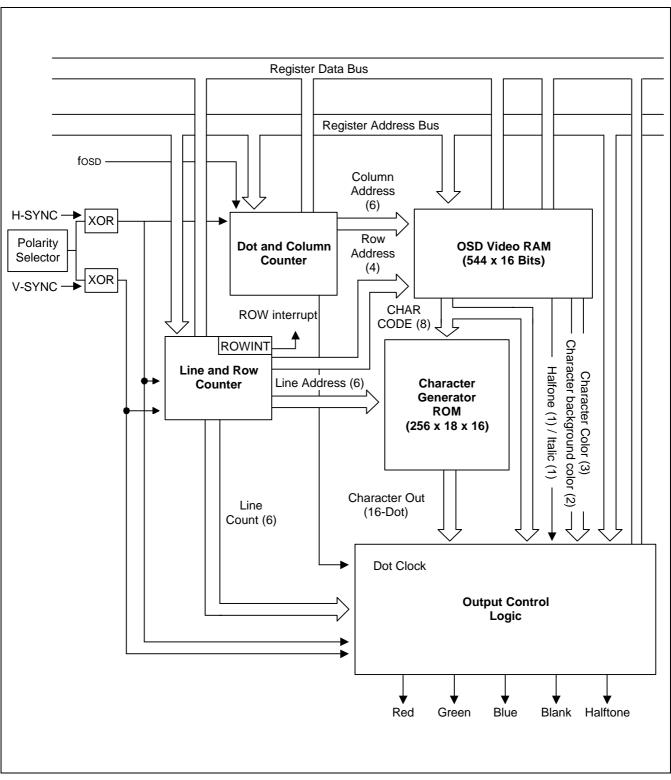

- On screen display module

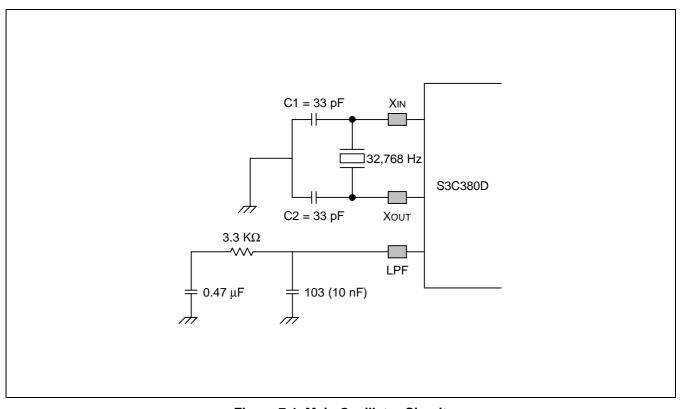

- Crystal/Ceramic oscillator or external clock can be used as the clock source

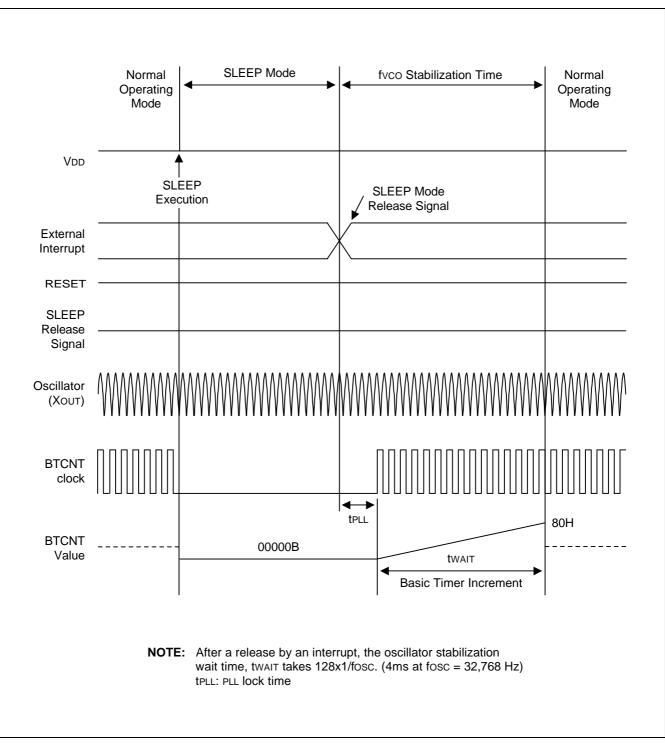

- Standby mode support: SLEEP mode

- One 8-bit basic timer and 3-bit watchdog timer

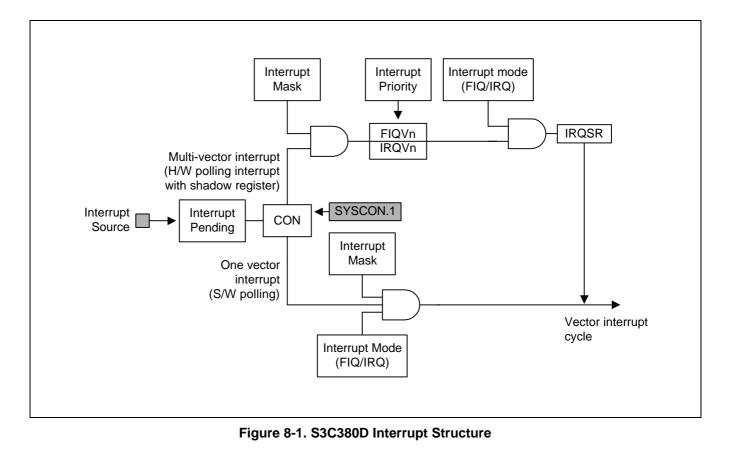

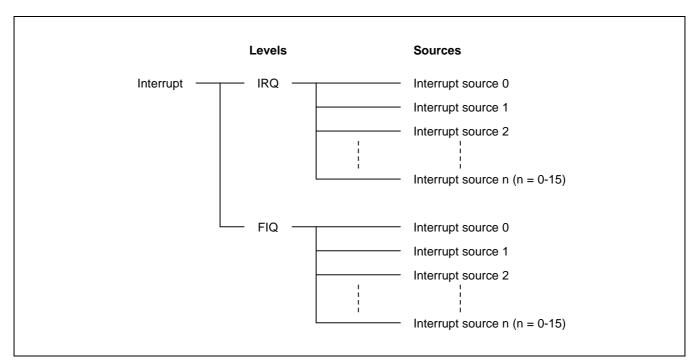

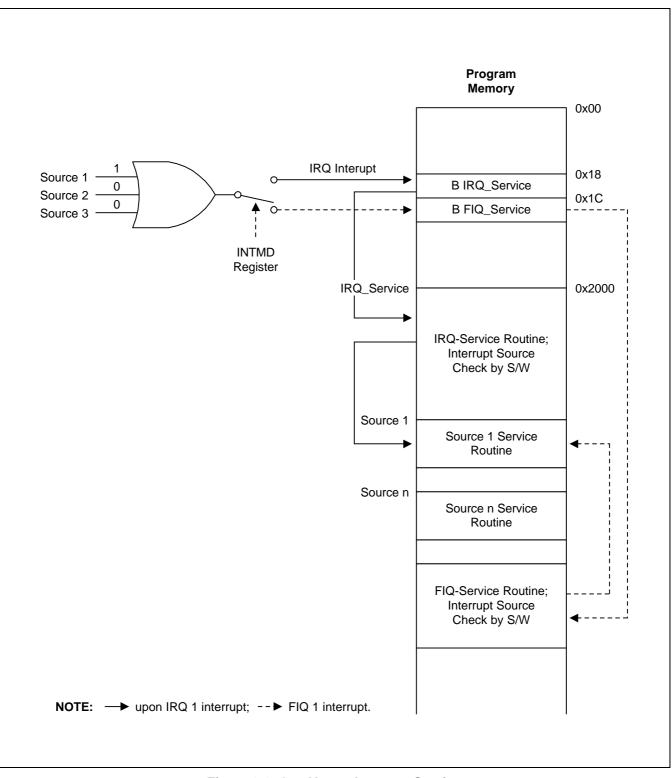

- Interrupt controller (16 interrupt sources and 2 vectors)

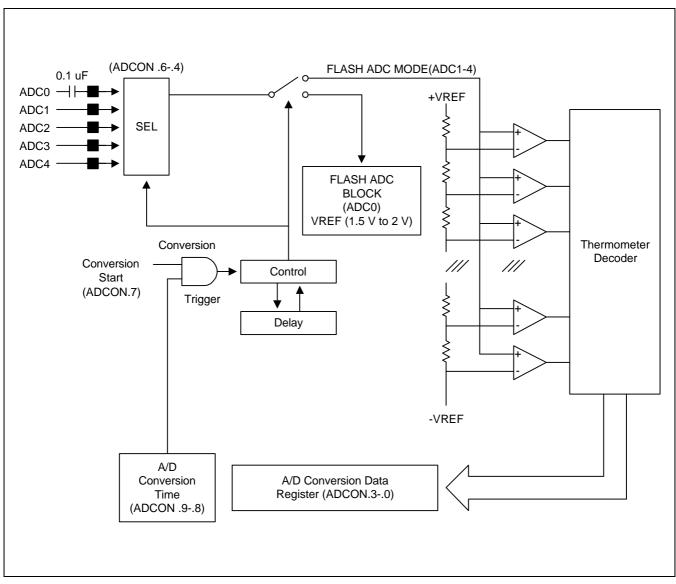

- Five 4-bit ADCs

- Four programmable I/O ports

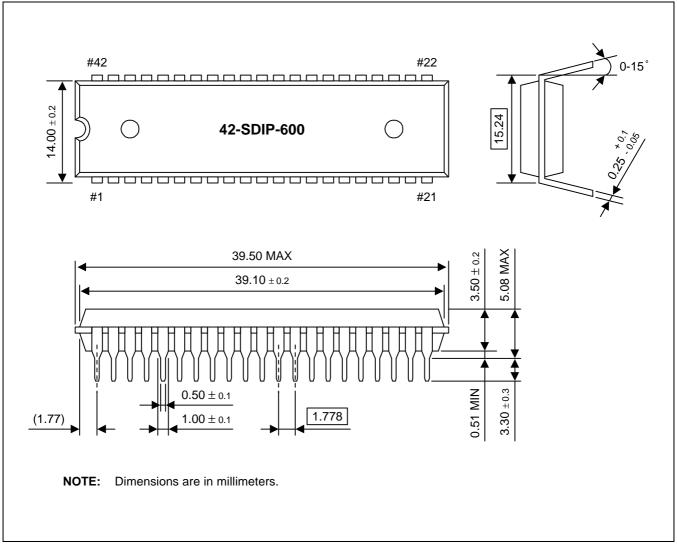

- 42-pin SDIP

# FEATURES

#### CPU

ARM7T CPU core

#### Memory

- 4-Kbyte RAM (3008-byte general purpose register area + 1088-byte OSD/CCD RAM)

- 128 Kbyte internal program memory

### General I/O

Four I/O ports (25 pins total) (6 V O/D: 3 pins, 5 V O/D: 4 pins)

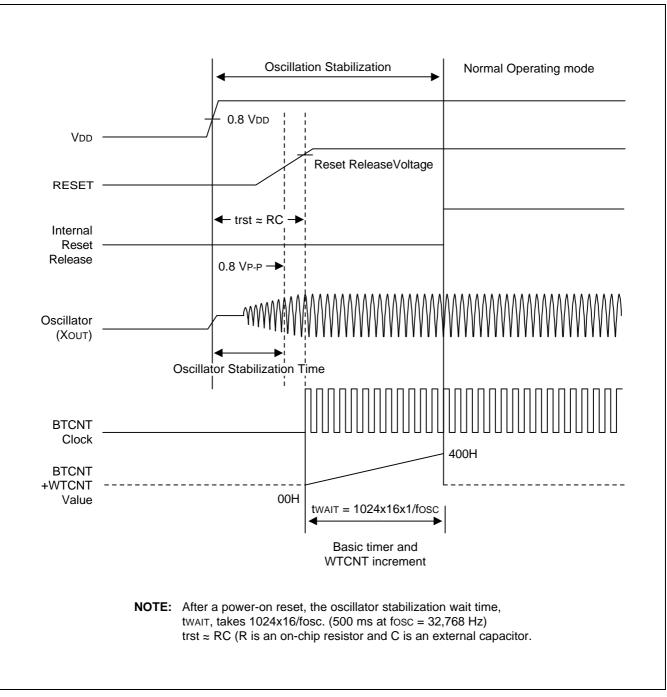

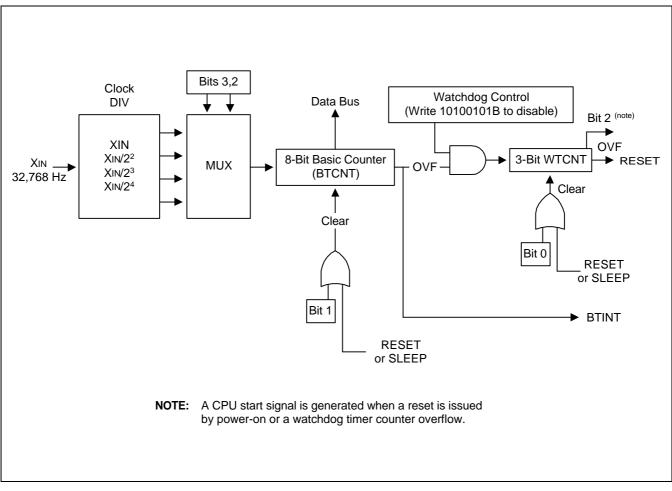

#### Basic timer and watchdog timer

- 8-bit counter + 3-bit counter

- Overflow signal of 8-bit counter makes a basic timer interrupt and control the oscillation warm-up time

- Overflow signal of 3-bit counter makes a system reset

#### **Timer/Counters**

• Three general purpose 16-bit timer/counters with interval timer modes

#### Interrupts

- 16 interrupt sources and 2 vectors

- Fast interrupt processing

- 2 interrupt shadow registers (32 bit × 2)

#### Pulse width modulation (PWM) module

• 14-bit PWM with 2-channel PWM counter

#### A/D converter

• 5-channel: 4-bit conversion resolution (flash ADC)

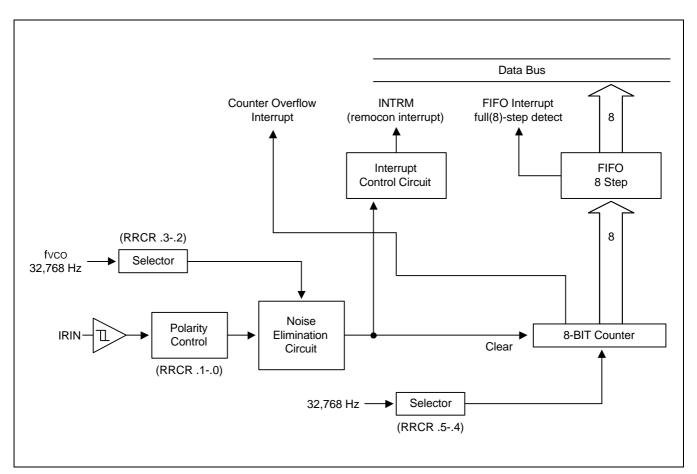

#### **Remocon receiver**

- FIFO 8 steps

- FIFO interrupt is full (8) step overflow

#### On screen display (OSD) mode

- Analog level OSD

- Halftone

- 64 character colors

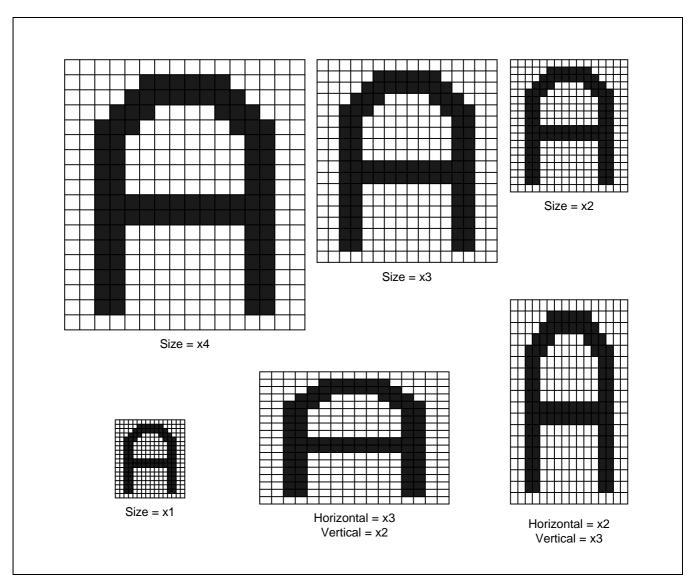

- 16 different character sizes

- Graphic OSD

- S/W CCD

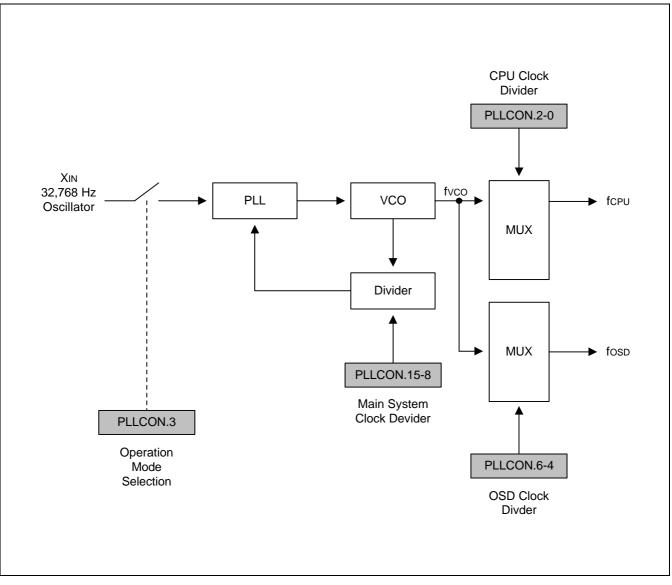

#### **Oscillator frequency**

- 32,768 Hz external crystal oscillator

- 1 Hz generation for real time clock

- PLL (Phase Lock Loop) controlled oscillators

- Maximum 16 MHz CPU clock

#### **Operating temperature Range**

• - 20 °C to + 85 °C

#### **Operating Voltage Range**

• 4.5 V to 5.5 V

#### Package Type

• 42-pin SDIP

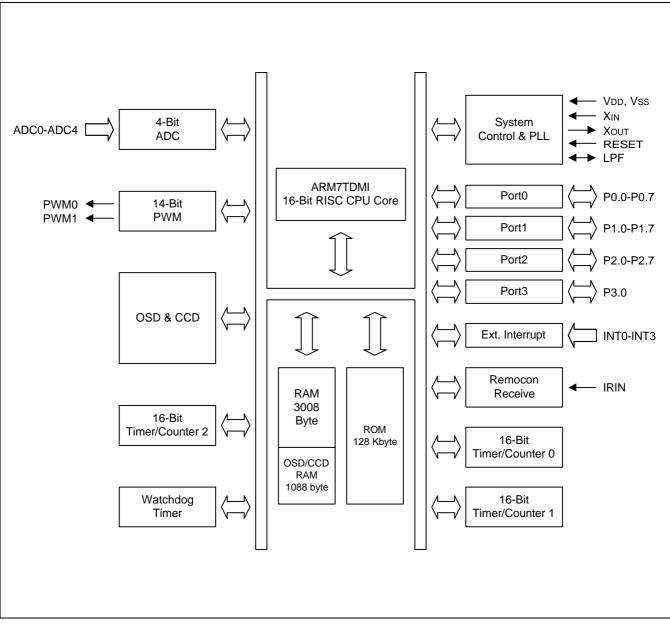

# **BLOCK DIAGRAM**

Figure 1-1. S3C380D Block Diagram

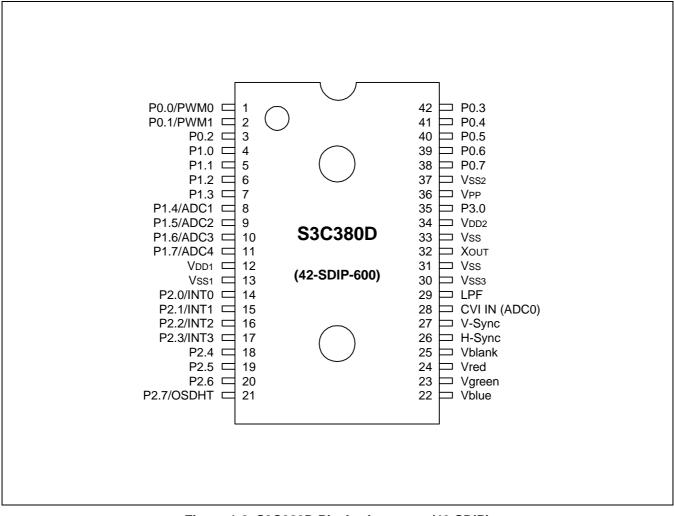

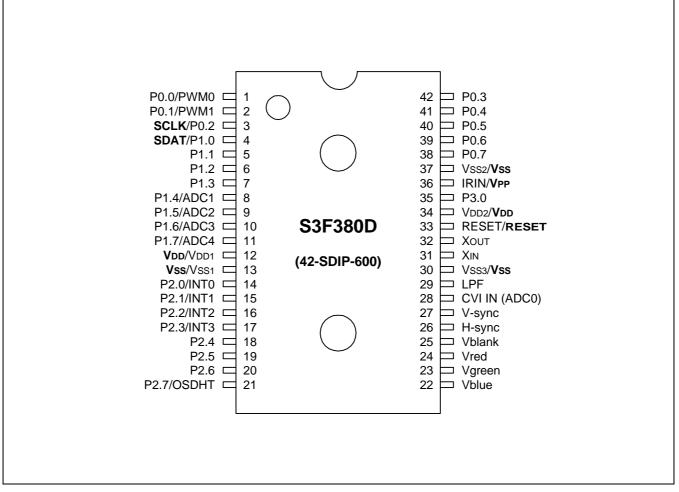

# **PIN ASSIGNMENTS**

Figure 1-2. S3C380D Pin Assignments (42-SDIP)

# **PIN DESCRIPTIONS**

| Pin Name          | Pin<br>Type | Pin Description                                                                                                                                                                                                  | Circuit<br>Type | Pin<br>Numbers | Share<br>Pins |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|

| P0.0              | I/O         | Input mode or push-pull output mode is<br>software configurable.<br>P0.0: PWM0 (14-bit PWM Output)                                                                                                               | 6               | 1              | PWM0          |

| P0.1-P0.2<br>P0.3 |             | General I/O Port (3-bit), Input or n-channel<br>open-drain output is software configurable.<br>Pins can withstand up to 6-volt loads. An<br>alternative function is supported.<br>P0.1: PWM1 (14-Bit PWM Output) | 3               | 2-3<br>42      | PWM1          |

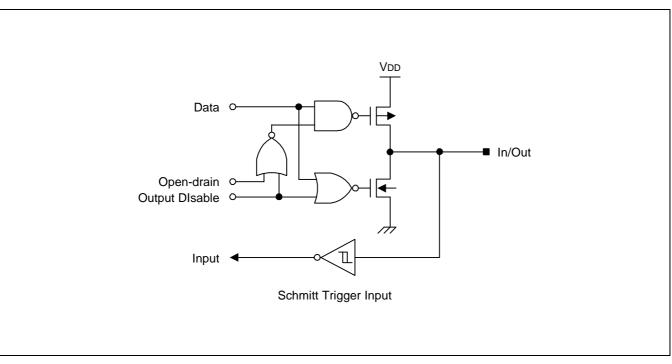

| P0.4-P0.7         |             | General I/O Port (4-bit), Input or Output<br>mode (push-pull or n-channel open drain) is<br>software configurable.                                                                                               | 7               | 38-41          |               |

| P1.0-P1.3         | I/O         | Input/output mode or push-pull output mode is software configurable.                                                                                                                                             | 6               | 4-7            |               |

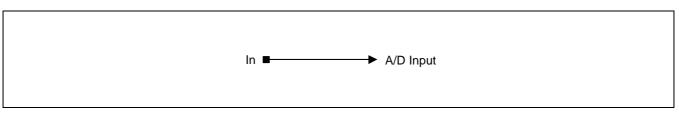

| P1.4-P1.7         |             | General I/O Port (4-bit), configurable for<br>digital input or n-channel open drain output.<br>P1.4-P1.7 can withstand up to 5-volt loads.<br>Multiplexed for alternative use as external<br>inputs ADC1-ADC4.   | 4               | 8-11           | ADC1-<br>ADC4 |

| P2.0-P2.3         | I/O         | General I/O Port (4-bit), input or push-pull<br>output mode is software configurable.<br>Multiplexed for alternative use as external<br>interrupt inputs INT0-INT3.                                              | 2               | 14-17          | INTO-INT3     |

| P2.4-P2.7         | I/O         | Input mode or push-pull output mode is<br>software configurable. An alternative<br>function is supported. P2.7: OSDHT<br>(Halftone signal output)                                                                | 6               | 18-21          | OSDHT         |

| P3.0              | I/O         | Input mode or push-pull output mode is software configurable.                                                                                                                                                    | 6               | 35             |               |

| PWM0              | 0           | Output pin for 14-bit PWM0 circuit                                                                                                                                                                               | 6               | 1              | P0.0          |

| PWM1              | 0           | Output pin for 14-bit PWM1 circuit                                                                                                                                                                               | 3               | 2              | P0.1          |

| ADC1-4            | I           | Input for 4-bit resolution flash A/D<br>Converter                                                                                                                                                                | 4               | 8-11           | P1.4-7        |

| INT0-INT3         | I           | External interrupt input pins                                                                                                                                                                                    | 2               | 14-17          | P2.0-3        |

| OSDHT             | 0           | Halftone control signal output for OSD                                                                                                                                                                           | 6               | 21             | P2.7          |

| IRIN              | I           | Remocon signal input<br>Normal mode: Remocon signal input<br>OTP Write mode: V <sub>PP</sub> =12.5 V                                                                                                             | 1               | 36             | _             |

| CVI IN            | I           | Video signal input                                                                                                                                                                                               | 8               | 28             | ADC0          |

# Table 1-1. S3C380D Pin Descriptions

| Pin Name                                              | Pin<br>Type | Pin Description                                               | Circuit<br>Type | Pin<br>Numbers         | Share<br>Pins |

|-------------------------------------------------------|-------------|---------------------------------------------------------------|-----------------|------------------------|---------------|

| RESET                                                 | I           | System reset input pin                                        | 9               | 33                     | _             |

| LPF                                                   | _           | PLL filter pin                                                | _               | 29                     | _             |

| H-SYNC                                                | I           | H-sync input for OSD and CCD                                  | 1               | 26                     | _             |

| V-SYNC                                                | I           | V-sync input for OSD and CCD                                  | 1               | 27                     | _             |

| V <sub>blank</sub>                                    | 0           | Video blank signal output for OSD and CCD                     | 5               | 25                     | -             |

| V <sub>red</sub>                                      | 0           | Red signal output for OSD and CCD                             | 5               | 24                     | -             |

| V <sub>green</sub>                                    | 0           | Green signal output for OSD and CCD                           | 5               | 23                     | -             |

| V <sub>blue</sub>                                     | 0           | Blue signal output for OSD and CCD                            | 5               | 22                     | -             |

| ADC0                                                  | I           | Input for 4-bit resolution flash<br>A/D Converter (1.5V-2.0V) | 8               | 28                     | CVI IN        |

| $V_{DD1}, V_{DD2}$<br>$V_{SS1}, V_{SS2}$<br>$V_{SS3}$ | _           | Power supply pins                                             | _               | 12, 34<br>13, 37<br>30 | -             |

| X <sub>IN</sub> , X <sub>OUT</sub>                    | I, O        | System clock pins (32,768 Hz)                                 | _               | 31,32                  | _             |

Table 1-1. S3C380D Pin Descriptions (Continued)

# **PIN CIRCUITS**

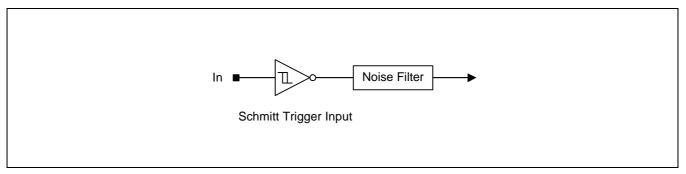

Figure 1-3. Pin Circuit Type 1 (H-Sync, V-Sync, IRIN)

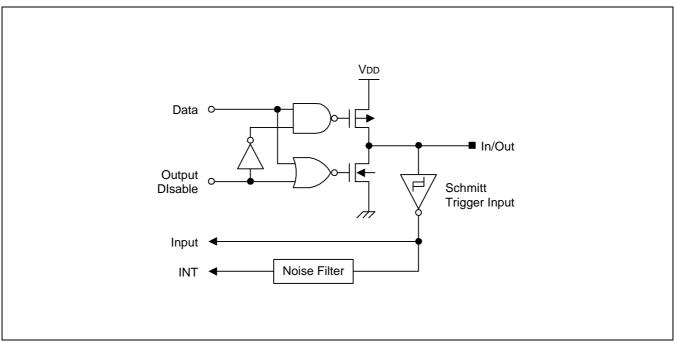

Figure 1-4. Pin Circuit Type 2 (P2.0-P2.3, INT0-INT3)

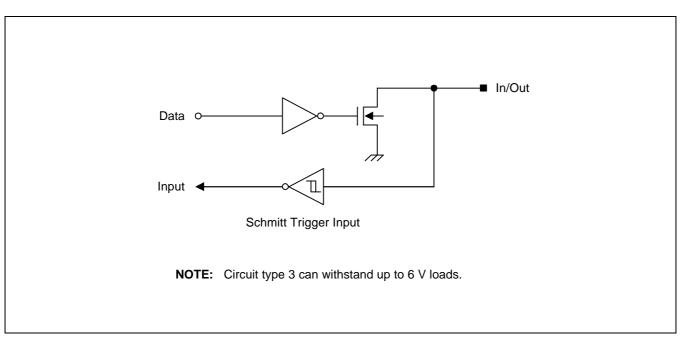

Figure 1-5. Pin Circuit Type 3 (P0.1-P0.3, PWM1)

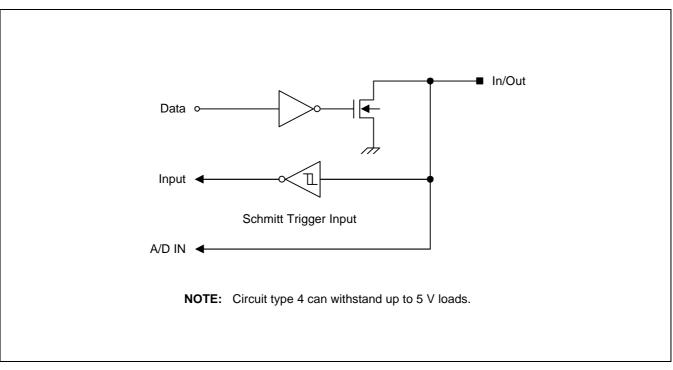

Figure 1-6. Pin Circuit Type 4 (P1.4-P1.7, ADC1-ADC4)

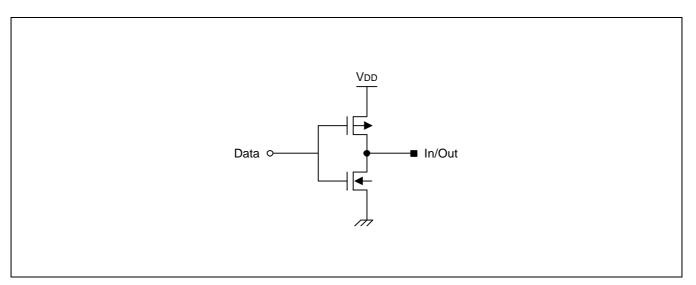

Figure 1-7. Pin Circuit Type 5 (V<sub>blue</sub>, V<sub>green</sub>, V<sub>red</sub>, V<sub>blank</sub>)

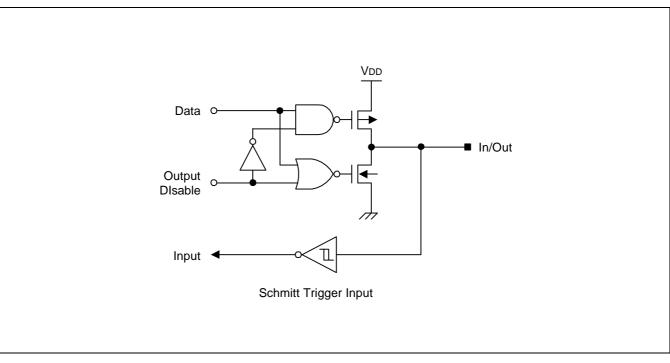

Figure 1-8. Pin Circuit Type 6 (P0.0, P1.0-P1.3, P2.4-P2.7, P3.0, OSDHT, PWM0)

Figure 1-10. Pin Circuit type 8 (CVI IN, ADC0)

Figure 1-11. Pin Circuit type 9 (RESET)

# **CPU CORE OVERVIEW**

The S3C380D CPU core is the ARM7TDMI processor, a general purpose, 32-bit microprocessor developed by Advanced RISC Machines, Ltd. (ARM). The core's architecture is based on Reduced Instruction Set Computer (RISC) principles. The RISC architecture makes the instruction set and its related decoding mechanisms simpler and more efficient than with microprogrammed Complex Instruction Set Computer (CISC) systems. The resulting benefit is high instruction throughput and impressive real-time interrupt response. Pipelining is also employed so that all components of the processing and memory systems can operate continuously. The ARM7TDMI has a 32-bit address bus.

An important feature of the ARM7TDMI processor, differentiating it from the ARM7 processor, is a unique architectural strategy called *THUMB*. The THUMB strategy is an extension of the basic ARM architecture and consists of 36 instruction formats. These formats are based on the standard 32-bit ARM instruction set, but have been re-coded using 16-bit wide opcodes.

Because THUMB instructions are one-half the bit width of normal ARM instructions, they produce very highdensity code. When a THUMB instruction is executed, its 16-bit opcode is decoded by the processor into its equivalent instruction in the standard ARM instruction set. The ARM core then processes the 16-bit instruction as it would a normal 32-bit instruction. In other words, the Thumb architecture gives 16-bit systems a way to access the 32-bit performance of the ARM core without incurring the full overhead of 32-bit processing.

Because the ARM7TDMI core can execute both standard 32-bit ARM instructions and 16-bit Thumb instructions, it lets you mix routines of Thumb instructions and ARM code in the same address space. In this way, you can adjust code size and performance, routine by routine, to find the best programming solution for a specific application.

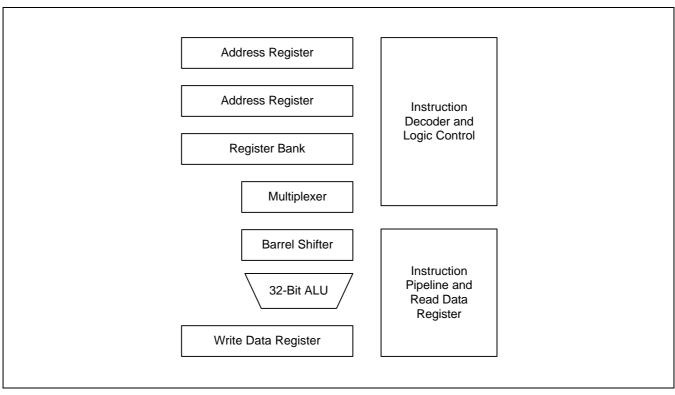

#### Figure 1-12. ARM7TDMI Core Block Diagram

# **INSTRUCTION SET**

The S3C380D instruction set is divided into two subsets: a standard 32-bit ARM instruction set and a 16-bit THUMB instruction set.

The 32-bit ARM instruction set is comprised of thirteen basic instruction types which can, in turn, be divided into four broad classes:

- Four types of branch instructions which control program execution flow, instruction privilege levels, and switching between ARM code and THUMB code.

- Three types of data processing instructions which use the on-chip ALU, barrel shifter, and multiplier to perform high-speed data operations in a bank of 31 registers (all with 32-bit register widths).

- Three types of load and store instructions which control data transfer between memory locations and the registers. One type is optimized for flexible addressing, another for rapid context switching, and the third for swapping data.

- Three types of co-processor instructions which are dedicated to controlling external co-processors. These instructions extend the off-chip functionality of the instruction set in an open and uniform way.

#### NOTE

All 32-bit ARM instructions can be executed conditionally.

The 16-bit THUMB instruction set contains 36 instruction formats drawn from the standard 32-bit ARM instruction set. The THUMB instructions can be divided into four functional groups:

- Four branch instructions.

- Twelve data processing instructions, which are a subset of the standard ARM data processing instructions.

- Eight load and store register instructions.

- Four load and store multiple instructions.

#### NOTE

Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with the identical processing model.

The 32-bit ARM instruction set and the 16-bit THUMB instruction sets are good targets for compilers of many different high-level languages. When assembly code is required for critical code segments, the ARM programming technique is straightforward, unlike that of some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

Pipelining is employed so that all parts of the processor and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

# **OPERATING STATES**

From a programmer's point of view, the ARM7TDMI core is always in one of two operating states. These states, which can be switched by software or by exception processing, are:

- ARM state (when executing 32-bit, word-aligned, ARM instructions), and

- *THUMB state* (when executing 16-bit, half-word aligned THUMB instructions).

### **OPERATING MODES**

The ARM7TDMI core supports seven operating modes:

- User mode: the normal program execution state

- FIQ (Fast Interrupt Request) mode: for supporting a specific data transfer or channel process

- IRQ (Interrupt ReQuest) mode: for general purpose interrupt handling

- Supervisor mode: a protected mode for the operating system

- Abort mode: entered when a data or instruction pre-fetch is aborted

- System mode: a privileged user mode for the operating system

- Undefined mode: entered when an undefined instruction is executed

Operating mode changes can be controlled by software, or they can be caused by external interrupts or exception processing. Most application programs execute in User mode. Privileged modes (that is, all modes other than User mode) are entered to service interrupts or exceptions, or to access protected resources.

# REGISTERS

The S3C380D CPU core has a total of 37 registers: 31 general-purpose, 32-bit registers, and 6 status registers. Not all of these registers are always available. Which registers are available to the programmer at any given time depends on the current processor operating state and mode.

#### NOTE

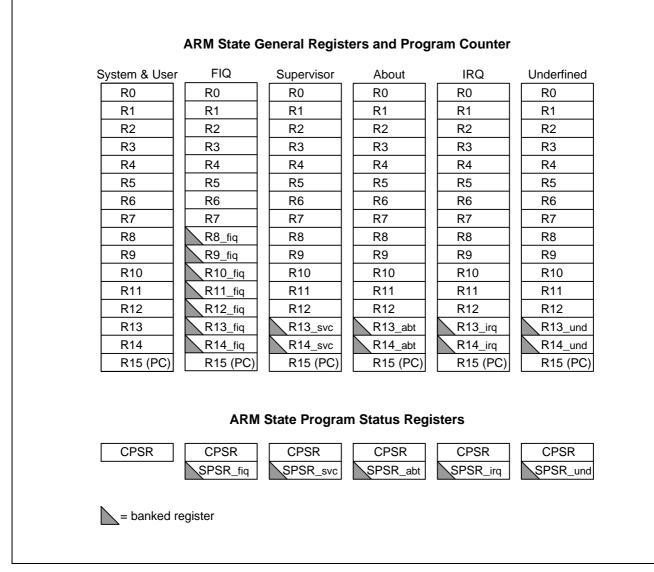

When the S3C380D is operating in ARM state, 16 general registers and one or two status registers can be accessed at any time. In privileged mode, mode-specific banked registers are switched in.

Two register sets, or banks, can also be accessed, depending on the core's current state: the *ARM state register* set and the *THUMB state register set*:

- The ARM state register set contains 16 directly accessible registers: R0-R15. All of these registers, except for R15, are for general-purpose use, and can hold either data or address values. An additional (seventeenth) register, the CPSR (Current Program Status Register), is used to store status information.

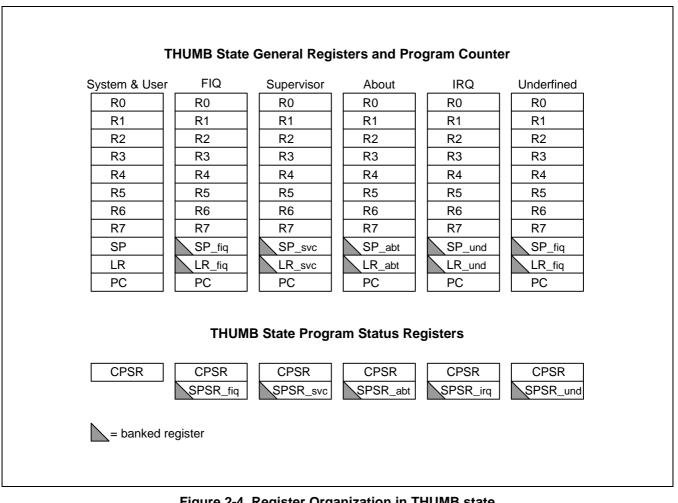

- The THUMB state register set is a subset of the ARM state set. You can access eight general registers, R0-R7, as well as the program counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. Each privileged mode has a corresponding banked stack pointer, link register, and saved process status register (SPSR).

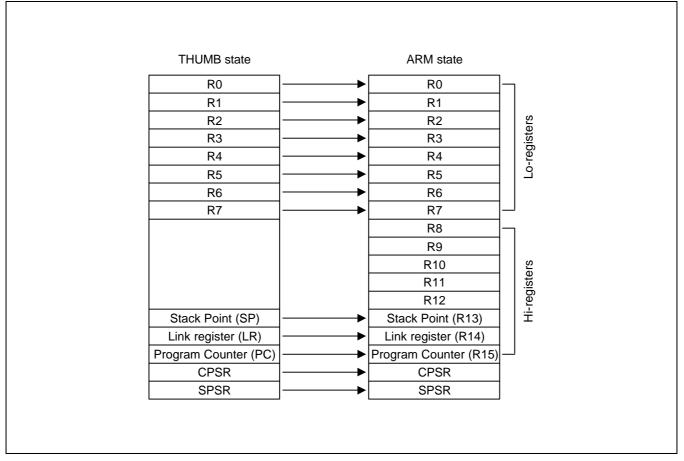

The THUMB state registers are related to the ARM state registers as follows:

- THUMB state R0-R7 registers and ARM state R0-R7 registers are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP, LR, and PC map directly to ARM state registers R13, R14, and R15, respectively

In THUMB state, registers R8-R15 are not part of the standard register set. However, you can access them for assembly language programming and use them for fast temporary storage, if necessary.

# **EXCEPTIONS**

An *exception* arises whenever the normal flow of program execution is interrupted. For example, when processing must be diverted to handle an interrupt from a peripheral. The processor's state just prior to handling the exception must be preserved so that the program flow can be resumed when the exception routine is completed. Multiple exceptions may arise simultaneously.

To process exceptions, the S3C380D uses the banked core registers to save the current state. The old PC value and the CPSR contents are copied into the appropriate R14 (LR) and SPSR register. The PC and mode bits in the CPSR are forced to a value which corresponds to the type of exception being processed.

The S3C380D core supports seven types of exceptions. Each exception has a fixed priority and a corresponding privileged processor mode, as shown in Table 1-2.

| Exception             | Mode on Entry   | Priority    |

|-----------------------|-----------------|-------------|

| Reset                 | Supervisor mode | 1 (Highest) |

| Data abort            | Abort mode      | 2           |

| FIQ                   | FIQ mode        | 3           |

| IRQ                   | IRQ mode        | 4           |

| Prefetch abort        | Abort mode      | 5           |

| Undefined instruction | Undefined mode  | 6 (Lowest)  |

| Software interrupt    | Supervisor mode | 6 (Lowest)  |

#### Table 1-2. S3C380D CPU Exceptions

# 2 PROGRAMMER'S MODEL

# OVERVIEW

The S3C380D was developed using the advanced ARM7TDMI core designed by Advanced RISC Machines, Ltd.

#### **PROCESSOR OPERATING STATES**

From the programmer's point of view, the ARM7TDMI can be in one of the following two states:

- ARM state which executes 32-bit, word-aligned ARM instructions.

- *THUMB state* which operates with 16-bit, halfword-aligned THUMB instructions. In this state, the PC uses bit 1 to select among alternate halfwords.

#### NOTE

Transition between these two states does not affect the processor mode or the contents of the registers.

#### SWITCHING STATE

#### **Entering THUMB State**

Entry into THUMB state can be achieved by executing a BX instruction with the state bit (bit 0) set in the operand register.

Transition to THUMB state will also occur automatically on return from an exception (IRQ, FIQ, UNDEF, ABORT, SWI etc.), if the exception was entered with the processor in THUMB state.

#### Entering ARM State

Entry into ARM state happens:

- On execution of the BX instruction with the state bit clear in the operand register.

- On the processor taking an exception (IRQ, FIQ, RESET, UNDEF, ABORT, SWI etc.). In this case, the PC is placed in the exception mode's link register, and execution commences at the exception's vector address.

#### **MEMORY FORMATS**

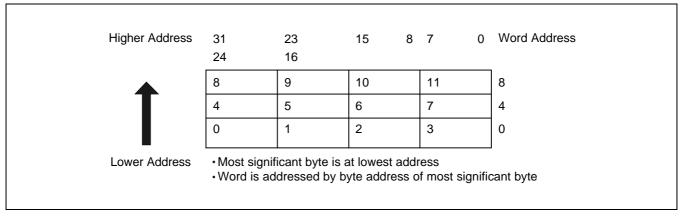

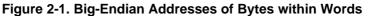

ARM7TDMI views memory as a linear collection of bytes numbered upwards from zero. Bytes 0 to 3 hold the first word stored, bytes 4 to 7 the second, and so on. ARM7TDMI can treat words in memory as being stored either in Big-Endian or Little-Endian format.

#### NOTE

The S3C380D is configured to Little-Endian format.

#### **BIG-ENDIAN FORMAT**

In Big-Endian format, the most significant byte of a word is stored at the lowest numbered byte and the least significant byte at the highest numbered byte. Byte 0 of the memory system is therefore connected to data lines 31 through 24.

#### LITTLE-ENDIAN FORMAT

In Little-Endian format, the lowest numbered byte in a word is considered the word's least significant byte, and the highest numbered byte the most significant. Byte 0 of the memory system is therefore connected to data lines 7 through 0.

Figure 2-2. Little-Endian Addresses of Bytes whthin Words

#### INSTRUCTION LENGTH

Instructions are either 32 bits (in ARM state) or 16 bits long (in THUMB state).

#### Data Types

ARM7TDMI supports byte (8-bit), halfword (16-bit), and word (32-bit) data types. Words must be aligned to fourbyte boundaries and half words to two-byte boundaries.

#### **OPERATING MODES**

ARM7TDMI supports seven modes of operation:

- User (usr): The normal ARM program execution state

- FIQ (fig): Designed to support a data transfer or channel process

- IRQ (irq): Used for general-purpose interrupt handling

- Supervisor (svc): Protected mode for the operating system

- Abort mode (abt): Entered after a data or instruction prefetch abort

- System (sys): A privileged user mode for the operating system

- Undefined (und): Entered when an undefined instruction is executed

Mode changes may be made under software control, or may be brought about by external interrupts or exception processing. Most application programs execute in User mode. The non-user modes-known as privileged modes-are entered in order to service interrupts or exceptions, or to access protected resources.

#### REGISTERS

ARM7TDMI has a total of 37 registers - 31 general-purpose 32-bit registers and six status registers - but all these cannot be seen at once. The processor state and operating mode dictate which registers are available to the programmer.

#### The ARM State Register Set

In ARM state, 16 general registers and one or two status registers are visible at any one time. In privileged (non-User) modes, mode-specific banked registers are switched in. Figure 2-3 shows which registers are available in each mode: the banked registers are marked with a shaded triangle.

The ARM state register set contains 16 directly accessible registers: R0 to R15. All of these except R15 are general-purpose, and may be used to hold either data or address values. In addition to these, there is a seventeenth register used to store status information.

| Register 14 | is used as the subroutine link register. This receives a copy of R15 when a Branch<br>and Link (BL) instruction is executed. At all other times it may be treated as a<br>general-purpose register. The corresponding banked registers R14_svc, R14_irq,<br>R14_fiq, R14_abt and R14_und are similarly used to hold the return values of R15<br>when interrupts and exceptions arise, or when Branch and Link instructions are<br>executed within interrupt or exception routines. |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register 15 | holds the Program Counter (PC). In ARM state, bits [1:0] of R15 are zero and bits [31:2] contain the PC. In THUMB state, bit [0] is zero and bits [31:1] contain the PC.                                                                                                                                                                                                                                                                                                           |

| Register 16 | is the CPSR (Current Program Status Register). This contains condition code flags and the current mode bits.                                                                                                                                                                                                                                                                                                                                                                       |

FIQ mode has seven banked registers mapped to R8-14 (R8\_fiq-R14\_fiq). In ARM state, many FIQ handlers do not need to save any register. User, IRQ, Supervisor, Abort and Undefined each have two banked registers mapped to R13 and R14, allowing each of these modes to have a private stack pointer and link registers.

Figure 2-3. Register Organization in ARM State

#### The THUMB State Register Set

The THUMB state register set is a subset of the ARM state set. The programmer has direct access to eight general registers, R0-R7, as well as the Program Counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. There are banked Stack Pointers, Link Registers and Saved Process Status Registers (SPSRs) for each privileged mode. This is shown in Figure 2-4.

Figure 2-4. Register Organization in THUMB state

#### The relationship between ARM and THUMB state registers

The THUMB state registers relate to the ARM state registers in the following way:

- THUMB state R0-R7 and ARM state R0-R7 are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP maps onto ARM state R13

- THUMB state LR maps onto ARM state R14

- The THUMB state Program Counter maps onto the ARM state Program Counter (R15)

This relationship is shown in Figure 2-5.

Figure 2-5. Mapping of THUMB State Registers onto ARM State Registers

#### Accessing Hi-Registers in THUMB State

In THUMB state, registers R8-R15 (the Hi registers) are not part of the standard register set. However, the assembly language programmer has limited access to them, and can use them for fast temporary storage.

A value may be transferred from a register in the range R0-R7 (a Lo register) to a Hi register, and from a Hi register to a Lo register, using special variants of the MOV instruction. Hi register values can also be compared with or added to Lo register values with the CMP and ADD instructions. For more information, refer to Figure 3-34.

### THE PROGRAM STATUS REGISTERS

The ARM7TDMI contains a Current Program Status Register (CPSR), plus five Saved Program Status Registers (SPSRs) for use by exception handlers. Their functions are as follows:

- Hold information about the most recently performed ALU operation

- Control enabling and disabling of interrupts

- Set the processor operating mode

The arrangement of bits is shown in Figure 2-6.

| cond    | dition | code | flags   | _          |                                      | (re   | sverv | ed) |   |        | _     |   |   | contro | ol bits |    |                        |               |

|---------|--------|------|---------|------------|--------------------------------------|-------|-------|-----|---|--------|-------|---|---|--------|---------|----|------------------------|---------------|

| ו<br>31 | 30     | 29   | 1<br>28 | ا<br>27    | 26                                   | 25    | 24    | 23  |   | 1<br>8 | <br>7 | 6 | 5 | 4      | 3       | 2  | 1                      | 1<br>0        |

| Ν       | z      | С    | V       | •          | •                                    | •     | •     | •   | ٠ | ٠      | I     | F | Т | M4     | M3      | M2 | M1                     | MO            |

|         |        |      |         | — c<br>— z | Dverflo<br>Carry/I<br>Zero<br>Vegati | Borro |       |     |   |        |       |   |   |        |         |    | Mode<br>State<br>FIQ c | bits<br>isabl |

Figure 2-6. Program Status Register Format

#### **The Condition Code Flags**

The N, Z, C and V bits are the condition code flags. These may be changed as a result of arithmetic and logical operations, and may be tested to determine whether an instruction should be executed.

In ARM state, all instructions may be executed conditionally: see Table 3-2 for details.

In THUMB state, only the Branch instruction is capable of conditional execution. See Figure 3-46 for details.

#### The Control Bits

The bottom 8 bits of a PSR (incorporating I, F, T and M[4:0]) are known collectively as the control bits. These will change when an exception arises. If the processor is operating in a privileged mode, they can also be manipulated by software.

The T bit

This reflects the operating state. When this bit is set, the processor is executing in THUMB state, otherwise it is executing in ARM state. This is reflected on the TBIT external signal. Note that the software must never change the state of the TBIT in the CPSR. Otherwise, the processor will enter an unpredictable state.

Interrupt disable bits

The I and F bits are the interrupt disable bits. When set, they disable the IRQ and FIQ interrupts respectively.

The M4, M3, M2, M1, and M0 bits (M[4:0]) are the mode bits. They determine the processor's operating mode, as shown in Table 2-1. Not all combinations of the mode bits define a valid processor mode. Only those explicitly described shall be used. The user should be aware that if any illegal value is programmed into the mode bits, M[4:0], the processor will enter an unrecoverable state. If this occurs, a reset should be applied.

| M[4:0] | Mode       | Visible THUMB state registers                  | Visible ARM atate registers                     |

|--------|------------|------------------------------------------------|-------------------------------------------------|

| 10000  | User       | R7R0,<br>LR, SP<br>PC, CPSR                    | R14R0,<br>PC, CPSR                              |

| 10001  | FIQ        | R7R0,<br>LR_fiq, SP_fiq<br>PC, CPSR, SPSR_fiq  | R7R0,<br>R14_fiqR8_fiq,<br>PC, CPSR, SPSR_fiq   |

| 10010  | IRQ        | R7R0,<br>LR_irq, SP_irq<br>PC, CPSR, SPSR_irq  | R12R0,<br>14_irqR13_irq,<br>PC, CPSR, SPSR_irq  |

| 10011  | Supervisor | R7R0,<br>LR_svc, SP_svc,<br>PC, CPSR, SPSR_svc | R12R0,<br>R14_svcR13_svc,<br>PC, CPSR, SPSR_svc |

| 10111  | Abort      | R7R0,<br>LR_abt, SP_abt,<br>PC, CPSR, SPSR_abt | R12R0,<br>R14_abtR13_abt,<br>PC, CPSR, SPSR_abt |

| 11011  | Undefined  | R7R0<br>LR_und, SP_und,<br>PC, CPSR, SPSR_und  | R12R0,<br>R14_undR13_und,<br>PC, CPSR           |

| 11111  | System     | R7R0,<br>LR, SP<br>PC, CPSR                    | R14R0,<br>PC, CPSR                              |

| Table 2-1. PSR Mode Bit Values |

|--------------------------------|

|--------------------------------|

#### Reserved bits

The remaining bits in the PSRs are reserved. When changing a PSR's flag or control bits, you must ensure that these unused bits are not altered. Also, your program should not rely on them containing specific values, since in future processors they may read as one or zero.

#### EXCEPTIONS

Exceptions arise whenever the normal flow of a program has to be halted temporarily, for example to service an interrupt from a peripheral. Before an exception can be handled, the current processor state must be maintained so that the original program can resume when the handler routine finishes.

It is possible for several exceptions to arise at the same time. If this happens, they are dealt with in a fixed order. See Exception Priorities on page 2-14.

#### Action on Entering an Exception

When handling an exception, the ARM7TDMI would do the following:

- 1. Contains the address of the next instruction in the appropriate Link Register. If the exception has been entered from ARM state, the address of the next instruction is copied into the Link Register (that is, current PC + 4 or PC + 8 depending on the exception. See Table 2-2 on for details). If the exception has been entered from THUMB state, the value written into the Link Register is the current PC offset by a value such that the program resumes from the correct place on return from the exception. This means that the exception handler does not need to determine which state the exception was entered from. For example, in the case of SWI, MOVS PC, R14\_svc will always return to the next instruction regardless of whether the SWI was executed in ARM or THUMB state.

- 2. Copies the CPSR into the appropriate SPSR

- 3. Forces the CPSR mode bits to a value which depends on the exception

- 4. Forces the PC to fetch the next instruction from the relevant exception vector

It may also set the interrupt disable flags to prevent otherwise unmanageable nestings of exceptions.

If the processor was in THUMB state when an exception occured, it would automatically switch into ARM state when the PC is loaded with the exception vector address.

#### Action on Leaving an Exception

On completion, the exception handler would do the following:

- 1. Moves the Link Register, minus an offset where appropriate, to the PC. (The offset will vary depending on the type of exception.)

- 2. Copies the SPSR back to the CPSR

- 3. Clears the interrupt disable flags, if they were set on entry

#### NOTE

An explicit switch back to THUMB state is never needed, since restoring the CPSR from the SPSR automatically sets the T bit to the value it held immediately prior to the exception.

#### **Exception Entry/Exit Summary**

Table 2-2 summarises the PC value contained in the relevant R14 on exception entry, and the recommended instruction for exiting the exception handler.

|       | Return Instruction   | Previou   | Previous State |   |  |  |

|-------|----------------------|-----------|----------------|---|--|--|

|       |                      | ARM R14_x | THUMB R14_x    |   |  |  |

| BL    | MOV PC, R14          | PC + 4    | PC + 2         | 1 |  |  |

| SWI   | MOVS PC, R14_svc     | PC + 4    | PC + 2         | 1 |  |  |

| UDEF  | MOVS PC, R14_und     | PC + 4    | PC + 2         | 1 |  |  |

| FIQ   | SUBS PC, R14_fiq, #4 | PC + 4    | PC + 4         | 2 |  |  |

| IRQ   | SUBS PC, R14_irq, #4 | PC + 4    | PC + 4         | 2 |  |  |

| PABT  | SUBS PC, R14_abt, #4 | PC + 4    | PC + 4         | 1 |  |  |

| DABT  | SUBS PC, R14_abt, #8 | PC + 8    | PC + 8         | 3 |  |  |

| RESET | NA                   | _         | _              | 4 |  |  |

| Table | 2-2  | Exception | Entry/E | xit        |

|-------|------|-----------|---------|------------|

| Table | L-L. | Exception |         | <b>AIL</b> |

#### NOTES:

1. Where PC is the address of the BL/SWI/Undefined Instruction fetch which had the prefetch abort.

2. Where PC is the address of the instruction which was not executed since the FIQ or IRQ took priority.

- 3. Where PC is the address of the Load or Store instruction which generated the data abort.

- 4. The value saved in R14\_svc upon reset is unpredictable.

#### FIQ

The FIQ (Fast Interrupt Request) exception is designed to support a data transfer or channel process, and in ARM state, it has sufficient private registers to remove the need for register saving (thus minimising the overhead of context switching).

FIQ is externally generated by taking the **nFIQ** input LOW. This input can except either synchronous or asynchronous transitions, depending on the state of the **ISYNC** input signal. When **ISYNC** is LOW, **nFIQ** and **nIRQ** are considered asynchronous, and a cycle delay for synchronization is incurred before the interrupt can affect the processor flow.

Irrespective of whether the exception was entered from ARM or Thumb state, a FIQ handler should leave the interrupt by executing

SUBS PC,R14\_fiq,#4

FIQ may be disabled by setting the CPSR's F flag (but note that this is not possible in User mode). If the F flag is clear, ARM7TDMI checks for a LOW level on the output of the FIQ synchroniser at the end of each instruction.

#### IRQ

The IRQ (Interrupt Request) exception is a normal interrupt caused by a LOW level on the **nIRQ** input. IRQ has a lower priority than FIQ and is masked out when an FIQ sequence is entered. It may be disabled at any time by setting the I bit in the CPSR, though this can only be done in a privileged (non-User) mode.

Irrespective of whether the exception was entered from ARM or Thumb state, an IRQ handler should return from the interrupt by executing

SUBS PC,R14\_irq,#4

#### Abort

An abort indicates that the current memory access cannot be completed. It can be signalled by the external **ABORT** input. ARM7TDMI checks for the abort exception during memory access cycles.

There are two types of abort:

- Prefetch abort: occurs during an instruction prefetch.

- Data abort: occurs during a data access.

If a prefetch abort occurs, the prefetched instruction is marked as invalid, but the exception will not be taken until the instruction reaches the head of the pipeline. If the instruction is not executed - for example because a branch occurs while it is in the pipeline - the abort does not take place.

If a data abort occurs, the action taken depends on the instruction type:

- Single data transfer instructions (LDR, STR) write back modified base registers: the abort handler must be aware of this.

- The swap instruction (SWP) is aborted as though it has not been executed.

- Block data transfer instructions (LDM, STM) complete. If write-back is set, the base is updated. If the

instruction would have overwritten the base with data (i.e. it has the base in the transfer list), the overwriting

is prevented. Any register overwriting is prevented after an abort is indicated, which means in particular that

R15 (always the last register to be transferred) is preserved in an aborted LDM instruction.

The abort mechanism allows the implementation of a demand paged virtual memory system. In such a system the processor is allowed to generate arbitrary addresses. When the data at an address is unavailable, the Memory Management Unit (MMU) signals an abort. The abort handler must then figure out the cause of the abort, make the requested data available, and retry the aborted instruction. The application program needs no knowledge of the amount of memory available to it, nor is its state in any way affected by the abort.

After resolving the cause of the abort, the handler should execute the following, irrespective of the state (ARM or Thumb):

| SUBS | PC,R14_abt,#4 | ; | for a prefetch abort, or |

|------|---------------|---|--------------------------|

| SUBS | PC,R14_abt,#8 | ; | for a data abort         |

This restores both the PC and the CPSR, and retries the aborted instruction.

#### Software Interrupt

The software interrupt instruction (SWI) is used for entering Supervisor mode, usually to request a particular supervisor function. A SWI handler should return by executing the following, irrespective of the state (ARM or Thumb):

MOV PC,R14\_svc

This restores the PC and the CPSR, and returns to the instruction following the SWI.

#### NOTE

nFIQ, nIRQ, ISYNC, LOCK, BIGEND, and ABORT pins exist only in the ARM7TDMI CPU core.

#### **Undefined Instruction**

When ARM7TDMI comes across an instruction which it cannot handle, it takes the undefined instruction trap. This mechanism may be used to extend either the THUMB or ARM instruction set by software emulation.

After emulating the failed instruction, the trap handler should execute the following, irrespective of the state (ARM or Thumb):

MOVS PC,R14\_und

This restores the CPSR and returns to the instruction following the undefined instruction.

#### **Exception Vectors**

The following table shows the exception vector addresses.

| Address   | Exception             | Mode in Entry |

|-----------|-----------------------|---------------|

| 0x0000000 | Reset                 | Supervisor    |

| 0x0000004 | Undefined instruction | Undefined     |

| 0x0000008 | Software Interrupt    | Supervisor    |

| 0x000000C | Abort (prefetch)      | Abort         |

| 0x0000010 | Abort (data)          | Abort         |

| 0x0000014 | Reserved              | Reserved      |

| 0x0000018 | IRQ                   | IRQ           |

| 0x000001C | FIQ                   | FIQ           |

#### **Table 2-3. Exception Vectors**

#### **Exception Priorites**

When multiple exceptions arise at the same time, a fixed priority system determines the order in which they are handled:

Highest priority:

- 1. Reset

- 2. Data abort

- 3. FIQ

- 4. IRQ

- 5. Prefetch abort

Lowest priority:

6. Undefined Instruction, Software interrupt.

#### Not All Exceptions Can Occur at Once:

Undefined Instruction and Software Interrupt are mutually exclusive, since they each correspond to particular (non-overlapping) decodings of the current instruction.

If a data abort occurs at the same time as a FIQ, and FIQs are enabled (i.e. the CPSR's F flag is clear), ARM7TDMI enters the data abort handler and then immediately proceeds to the FIQ vector. A normal return from FIQ will cause the data abort handler to resume execution. Placing data abort at a higher priority than FIQ is necessary to ensure that the transfer error does not avoid detection. The time for this exception entry should be added to worst-case FIQ latency calculations.

#### **INTERRUPT LATENCIES**

The worst case latency for FIQ, assuming that it is enabled, consists of the longest time the request can take to pass through the synchroniser (*Tsyncmax* if asynchronous), the time for the longest instruction to complete (*Tldm*, the longest instruction is an LDM which loads all the registers including the PC), the time for the data abort entry (*Texc*), plus the time for FIQ entry (*Tfiq*). At the end of this time, ARM7TDMI executes the instruction at 0x1C.

*Tsyncmax* is 3 processor cycles, *Tldm* is 20 cycles, *Texc* is 3 cycles, and *Tfiq* is 2 cycles. The total time is therefore 28 processor cycles. This is just over 1.4 microseconds in a system which uses a continuous 20 MHz processor clock. The maximum IRQ latency calculation is similar to this, but must allow for the fact that an FIQ has higher priority and could delay entry into the IRQ handling routine for an arbitrary length of time. The minimum latency for an FIQ or IRQ consists of the shortest time the request can take through the synchroniser (*Tsyncmin*) plus *Tfiq*. This is 4 processor cycles.

#### RESET

When the RESET signal goes LOW, ARM7TDMI abandons the executing instruction and continues to fetch instructions from incrementing word addresses.

When RESET goes HIGH again, ARM7TDMI would do the following:

- 1. Overwrites R14\_svc and SPSR\_svc by copying the current values of the PC and CPSR into them. The value of the saved PC and SPSR is not defined.

- 2. Forces M[4:0] to 10011 (Supervisor mode), sets the I and F bits in the CPSR, and clears the CPSR's T bit.

- 3. Forces the PC to fetch the next instruction from address 0x00.

- 4. Execution resumes in ARM state.

# 4 ADDRESS SPACES

# OVERVIEW

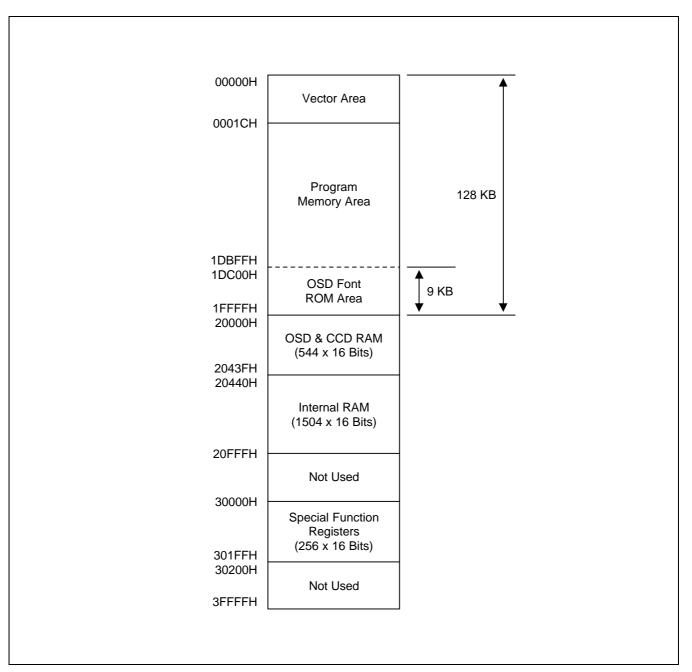

The S3C380D microcontroller has two kinds of address space:

- Internal program memory (ROM)

- Internal register file

The S3C380D has an on-chip 128-Kbyte mask-programmable ROM. An external memory interface is not implemented.

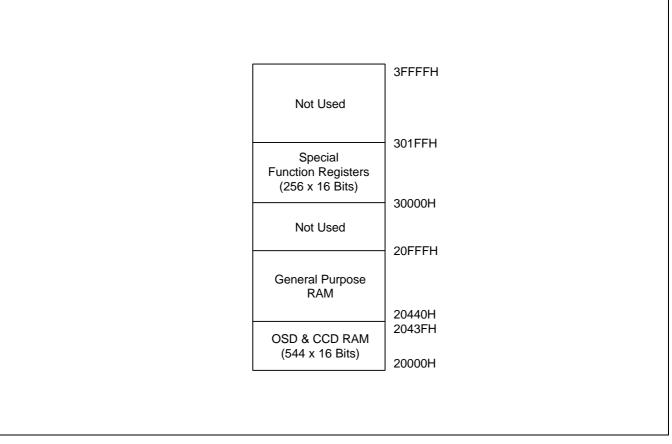

There are 1504 general-purpose 16-bit data registers in the register file. Forty two 16-bit registers are used for CPU, interrupt and system control. To support peripheral, I/O, and clock functions, there are 27 control registers and 9 data registers. In addition, there is a  $544 \times 16$ -bit area for on-screen display (OSD) video RAM.

Figure 4-1. S3C380D/F380D Memory Map

## **PROGRAM MEMORY (ROM)**

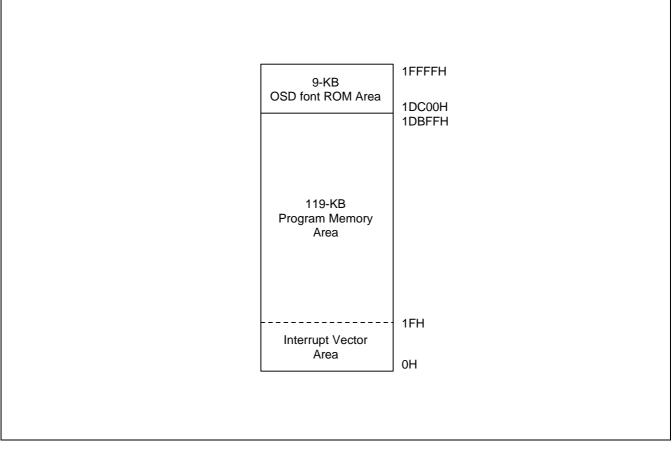

Program memory (ROM) stores program codes or table data. The S3C380D has a 128-Kbyte mask programmable program memory (1FFFFh).

As shown in Figure 2-1, the first 32 bytes of the ROM (0H-01FH) are reserved for interrupt vector addresses. Unused locations in this range can be used as normal program memory. When the vector address area is used to store normal program data, care must be taken to avoid overwriting vector addresses stored in these locations.

When you use S3C380D, the program memory is 128-Kbyte in total, including the 9-Kbyte OSD font ROM. If you use 9-Kbyte as the OSD font ROM area, you are able to use the remaining 119-Kbyte for program memory.

Figure 4-2. Program Memory Address Spaces

# **REGISTER ARCHITECTURE**

The special function register has 78 halfwords, and the address exists within 30000H-301FFH. The OSD & CCD RAM have 544 halfwords, and the address exists within 20000H-2043FH. The general-purpose RAM has 1504 halfwords, and the address exists within 20440-20FFFH.

| Register Type                     | Number of Bytes | Number of Half-word |

|-----------------------------------|-----------------|---------------------|

| General-purpose registers         | 3008            | 1504                |

| Special function registers        | 156             | 78                  |

| On-screen display (OSD) video RAM | 1088            | 544                 |

| Total Addressable Bytes           | 4152            | 2126                |

| Table 4-1. Regist | er Type Summary |

|-------------------|-----------------|

|-------------------|-----------------|

Figure 4-3. Internal Register File Organization

# **5** SPECIAL FUNCTION REGISTERS

# OVERVIEW

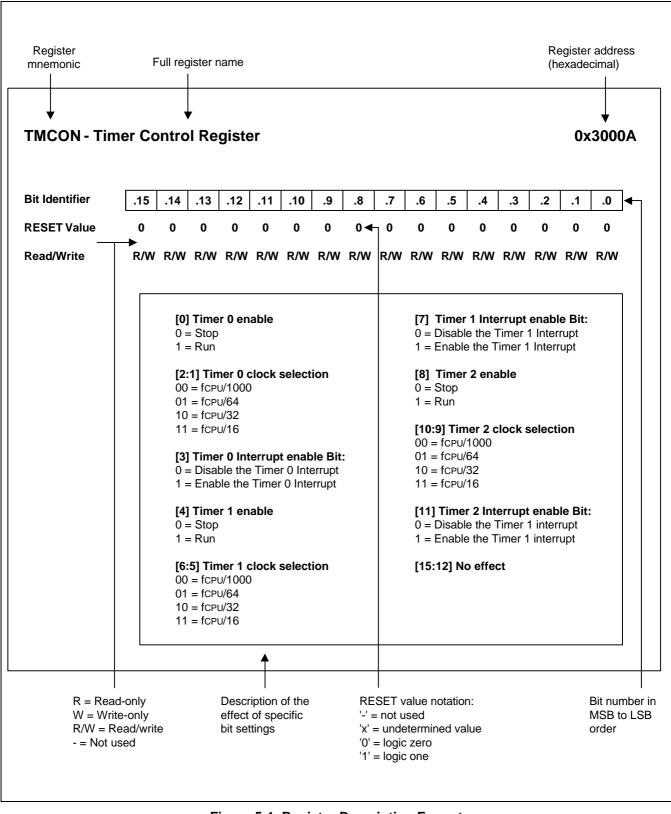

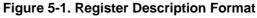

In this chapter, detailed descriptions of the S3C380D/F380D control registers are presented in an easy-to-read format. These descriptions will help familiarize you with the mapped locations in the register file. You can also use them as a quick-reference source when writing application programs.

System and peripheral registers are summarized in Tables 5-1. Figure 5-1 illustrates the important features of the standard register description format.

Control register descriptions are arranged in alphabetical order according to register mnemonic. More information about control registers is presented in the context of the various peripheral hardware descriptions in this manual.

#### S3C380D SPECIAL REGISTERS

| Group     | Registers     | Address | Description                      | R/W | Reset Value |

|-----------|---------------|---------|----------------------------------|-----|-------------|

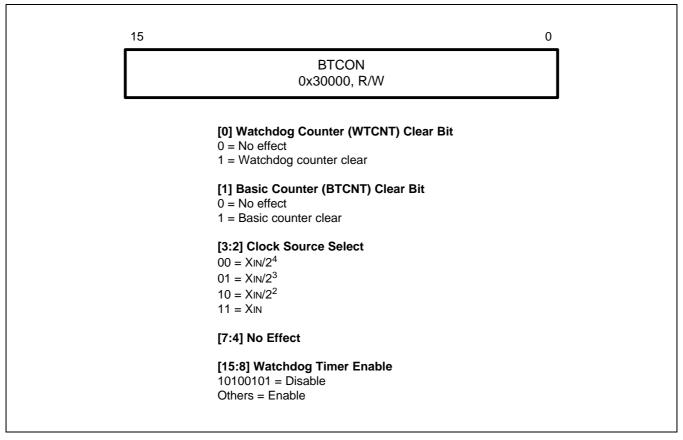

| Basic and | BTCON         | 0x30000 | Watchdog timer control register  | R/W | 0000h       |

| 16-bit    | BTCNT         | 0x30002 | Basic timer counter register     | R   | xx00h       |

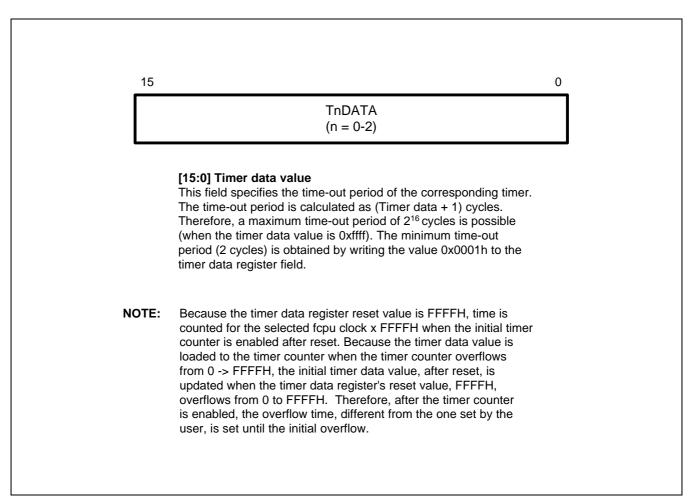

| timers    | <b>T0DATA</b> | 0x30004 | Timer 0 data register            | R/W | 0FFFFh      |

|           | T1DATA        | 0x30006 | Timer 1 data register            | R/W | 0FFFFh      |

|           | T2DATA        | 0x30008 | Timer 2 data register            | R/W | 0FFFFh      |

|           | TMCON         | 0x3000A | Timer control register           | R/W | 0000h       |

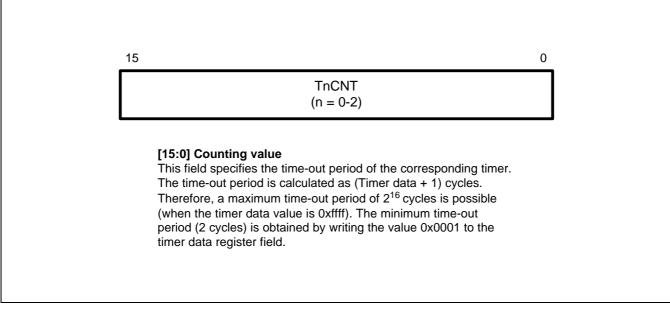

|           | T0CNT         | 0x3000C | Timer 0 counter register         | R   | xxxxh       |

|           | T1CNT         | 0x3000E | Timer 1 counter register         | R   | xxxxh       |

|           | T2CNT         | 0x30010 | Timer 2 counter register         | R   | xxxxh       |

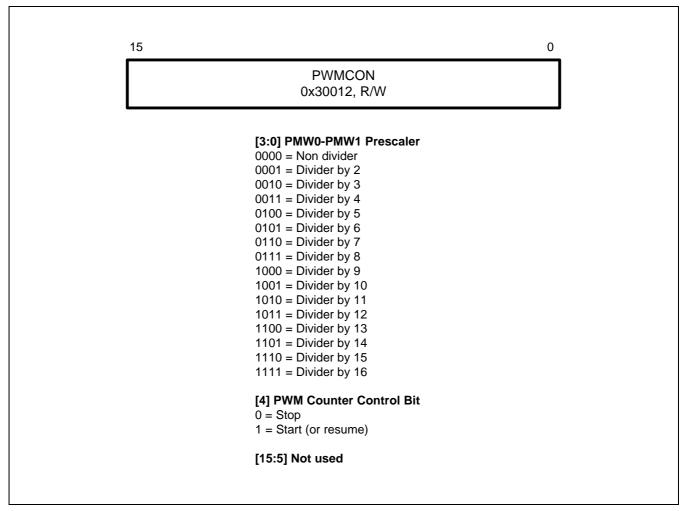

| PWM       | PWMCON        | 0x30012 | PWM control register             | R/W | xxx0h       |

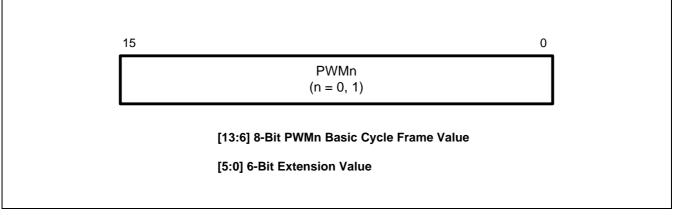

|           | PWM0          | 0x30014 | PWM 0 data register (14-bit)     | R/W | 3FC0h       |

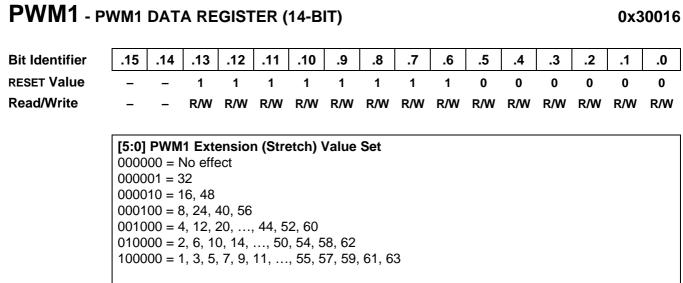

|           | PWM1          | 0x30016 | PWM 1 data register (14-bit)     | R/W | 3FC0h       |

| Remocon   | RRCR          | 0x30018 | Remocon receive control register | R/W | 0100h       |

| receive   | FIFOD         | 0x3001A | FIFO data register               | R   | xxxxh       |

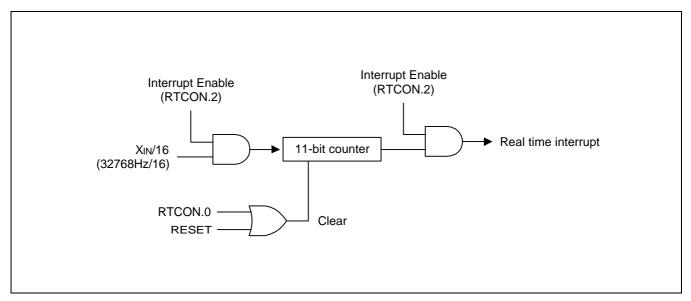

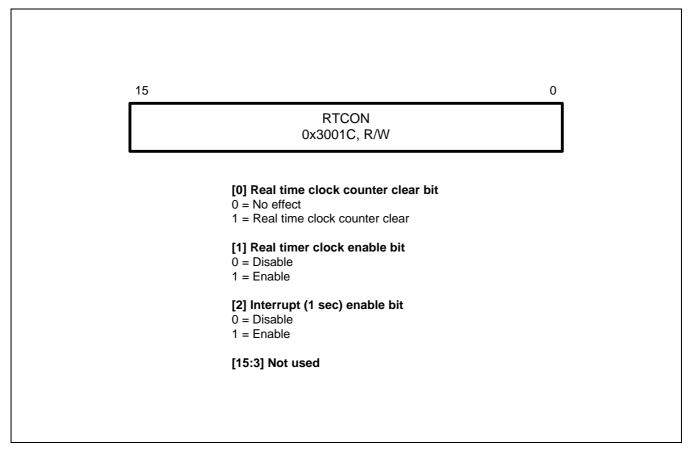

| Real time | RTCON         | 0x3001C | Real time clock control register | R/W | 0000h       |

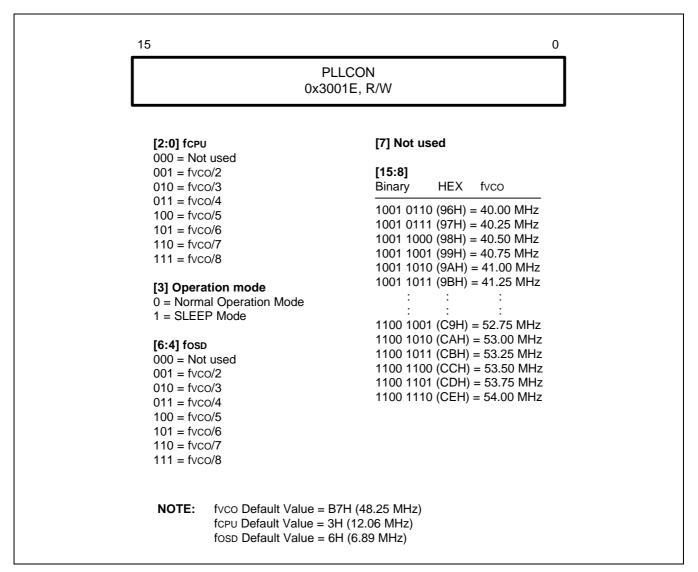

| PLL       | PLLCON        | 0x3001E | PLL clock control register       | R/W | B763h       |

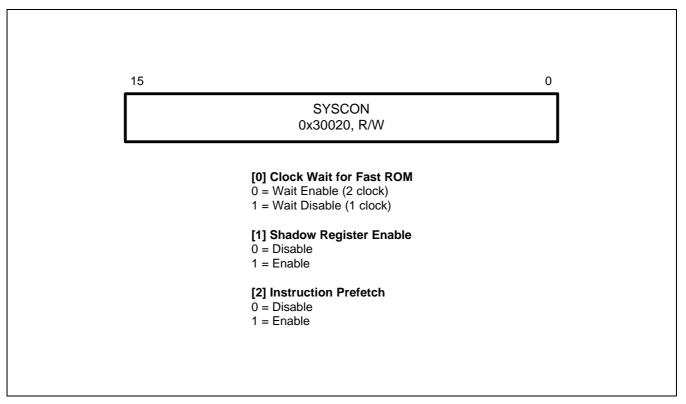

| System    | SYSCON        | 0x30020 | System control register          | R/W | 0000h       |

| Interrupt | INTPR         | 0x30022 | Interrupt pending register       | R/W | 0000h       |

|           | INTMD         | 0x30024 | Interrupt mode register          | R/W | 0000h       |

|           | INTMK         | 0x30026 | Interrupt mask register          | R/W | 0000h       |

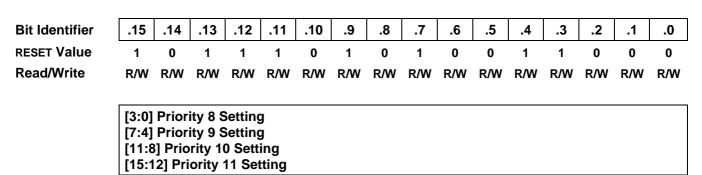

|           | IPR0          | 0x30028 | Interrupt priority register 0    | R/W | 3210h       |

|           | IPR1          | 0x3002A | Interrupt priority register 1    | R/W | 7654h       |

|           | IPR2          | 0x3002C | Interrupt priority register 2    | R/W | BA98h       |

|           | IPR3          | 0x3002E | Interrupt priority register 3    | R/W | FEDCH       |

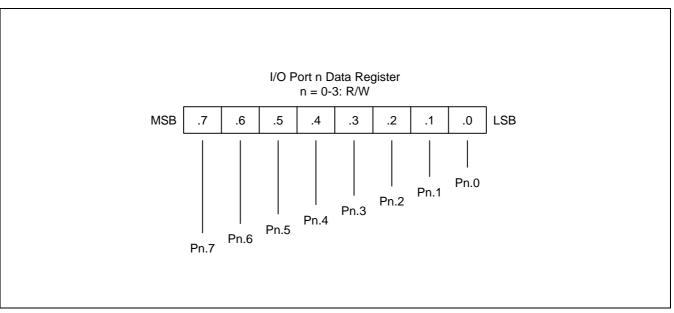

| I/O ports | P0            | 0x30030 | Port0 data register              | R/W | xx00h       |

|           | P1            | 0x30031 | Port1 data register              | R/W | 00xxh       |

|           | P2            | 0x30032 | Port2 data register              | R/W | xx00h       |

|           | P3            | 0x30033 | Port3 data register              | R/W | 00xxh       |

|           | P0CON         | 0x30034 | Port0 control register           | R/W | 0000h       |

|           | P1CON         | 0x30036 | Port1 control register           | R/W | 0000h       |

|           | P2CON         | 0x30038 | Port2 control register           | R/W | 0000h       |

|           | P3CON         | 0x3003A | Port3 control register           | R/W | xxx0h       |

#### Table 5-1. Special Registers

| Group     | Registers   | Address | Description                         | R/W | Reset Value |

|-----------|-------------|---------|-------------------------------------|-----|-------------|

| ADC       | ADCON       | 0x3003C | A/D conversion mode register        | R/W | x000h       |

| _         | TSTC (note) | 0x3003E | Test control register               | -   | _           |

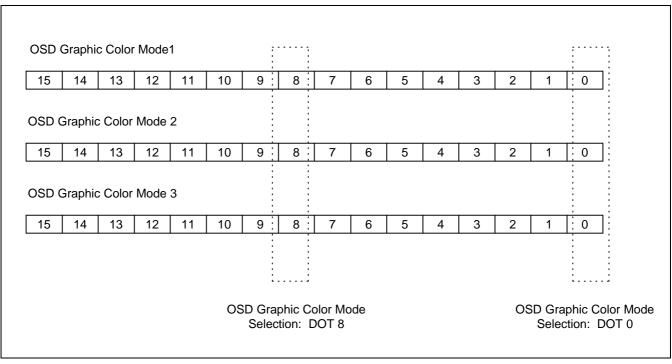

| On screen | OSGM3       | 0x30040 | OSD graphic color mode 3            | R/W | 0000h       |

| display   | OSGM2       | 0x30042 | OSD graphic color mode 2            | R/W | 0000h       |

|           | OSGM1       | 0x30044 | OSD graphic color mode 1            | R/W | 0000h       |

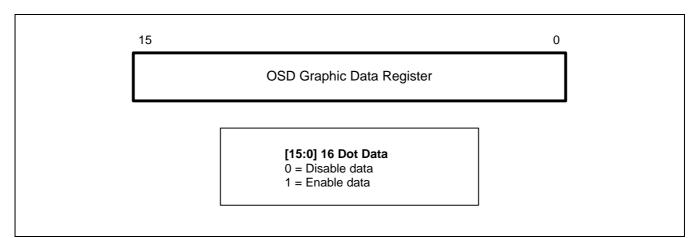

|           | OSGDATA     | 0x30046 | OSD graphic color data              | R/W | 0000h       |

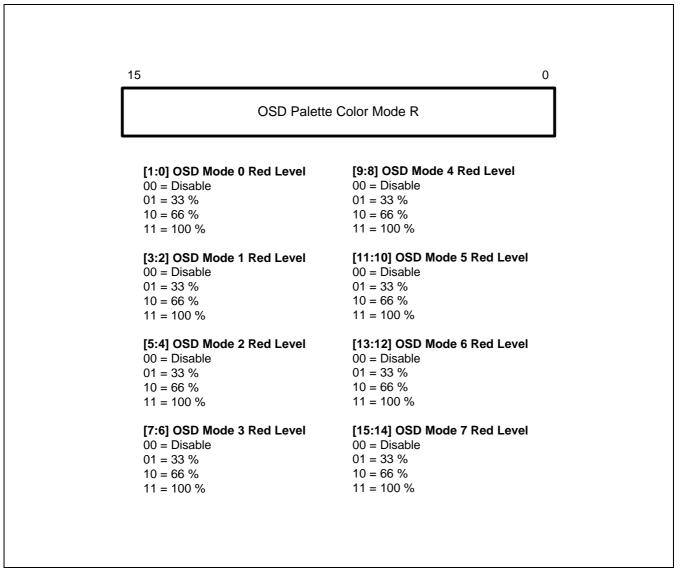

|           | OSDPLTR     | 0x30048 | OSD palette color mode R            | R/W | FF00h       |

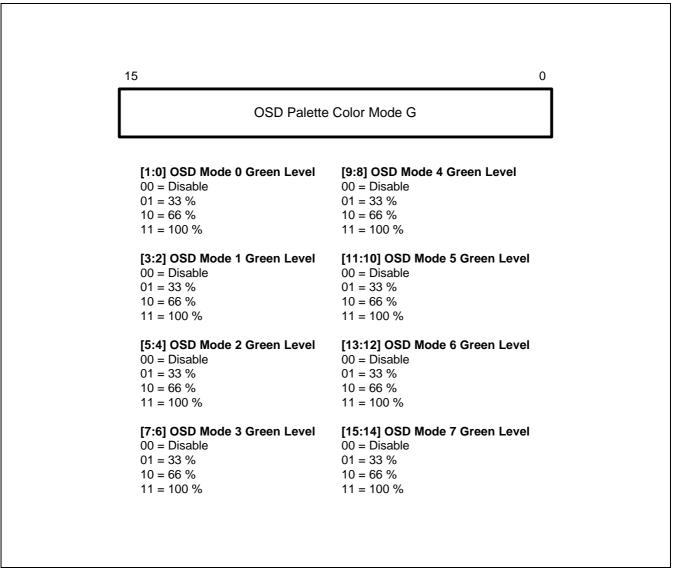

|           | OSDPLTG     | 0x3004A | OSD palette color mode G            | R/W | F0F0h       |

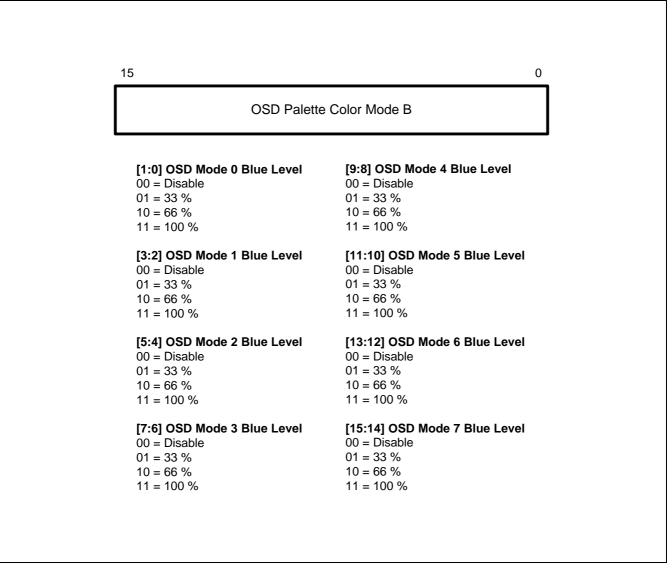

|           | OSDPLTB     | 0x3004C | OSD palette color mode B            | R/W | CCCCh       |

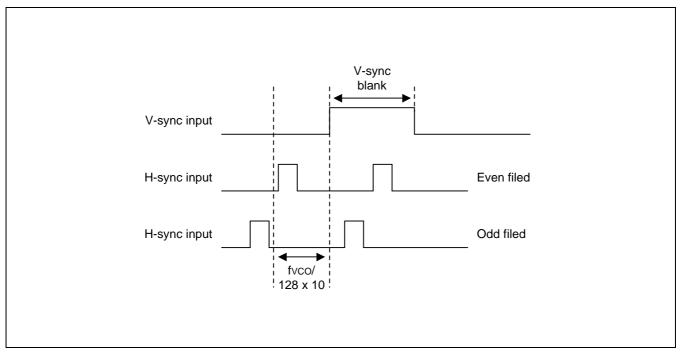

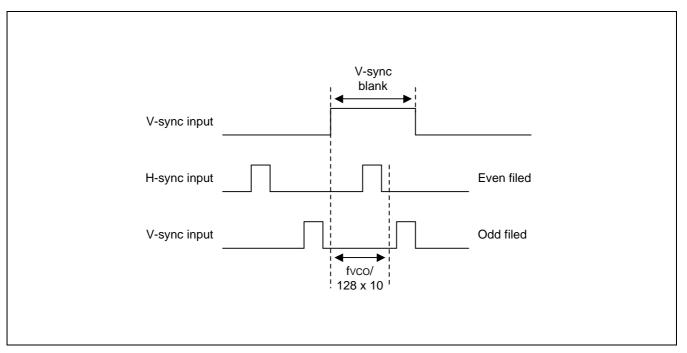

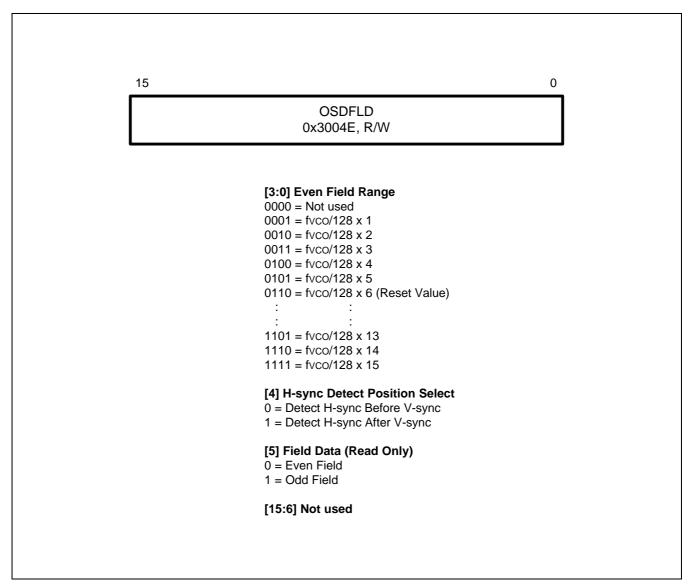

|           | OSDFLD      | 0x3004E | OSD field control register          | R/W | 0006h       |

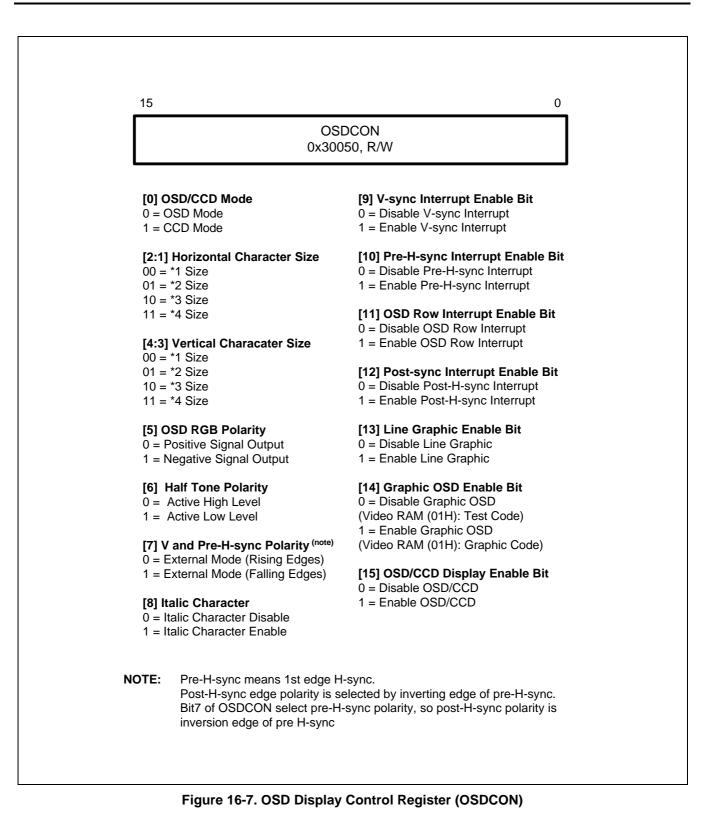

|           | OSDCON      | 0x30050 | OSD control register                | R/W | 0000h       |

|           | FADECON     | 0x30052 | OSD FADE control register           | R/W | 0000h       |

|           | OSDBGD      | 0x30054 | OSD background color register       | R/W | 0000h       |

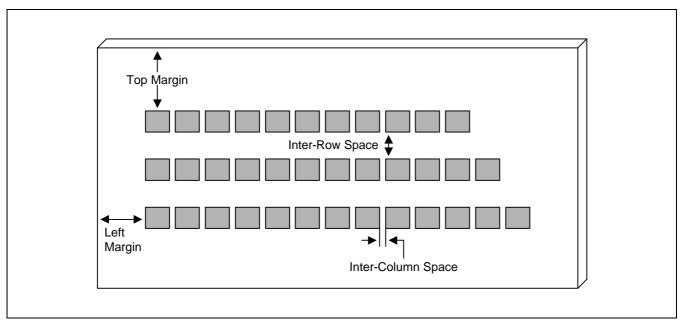

|           | OSDVMGN     | 0x30056 | OSD margin control register         | R/W | 2400h       |

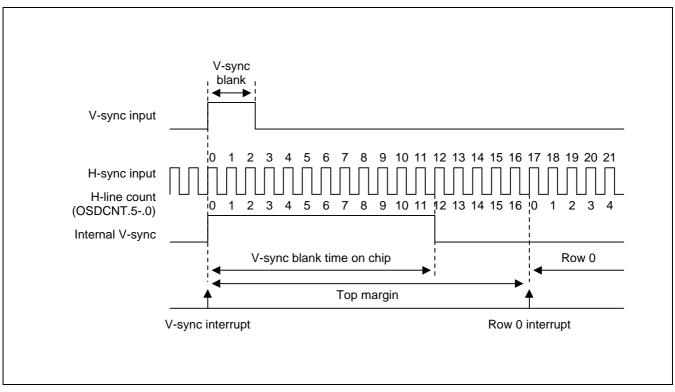

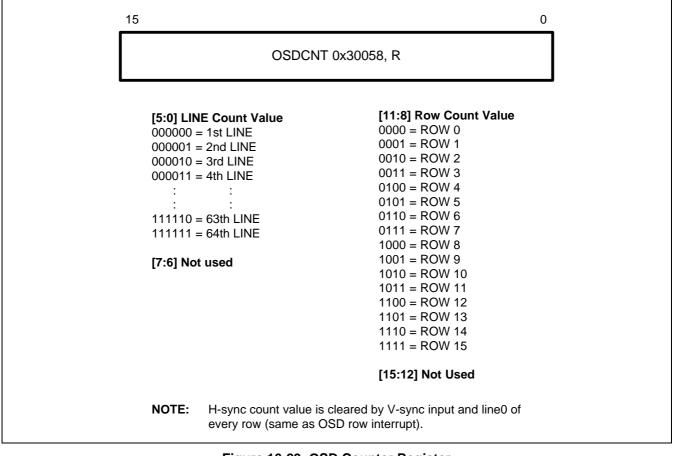

|           | OSDCNT      | 0x30058 | OSD counter register                | R/W | xxxxh       |

|           |             | Locati  | on 0x3005A - 0x3005F are not mapped |     | -           |

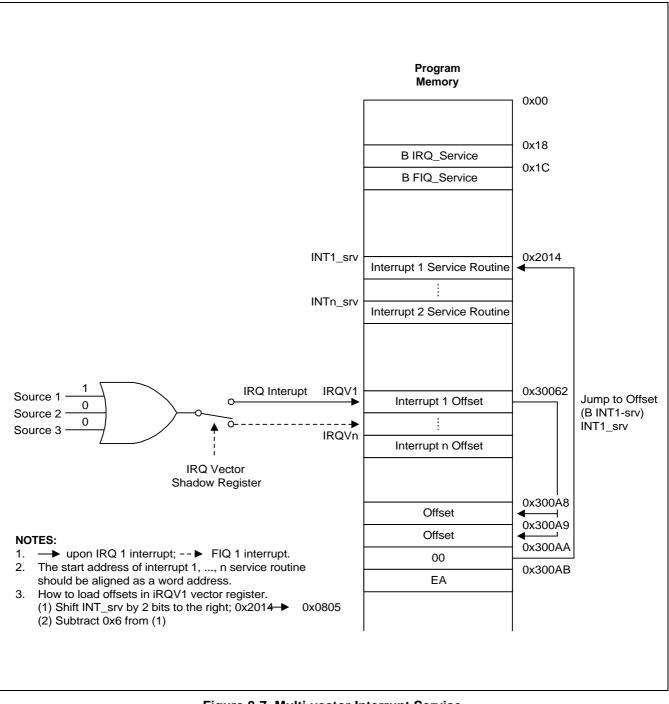

| Interrupt | IRQV0       | 0x30060 | IRQ vector register0                | R/W | 0000h       |

|           | IRQV1       | 0x30062 | IRQ vector register1                | R/W | 0000h       |

|           | IRQV2       | 0x30064 | IRQ vector register2                | R/W | 0000h       |

|           | IRQV3       | 0x30066 | IRQ vector register3                | R/W | 0000h       |

|           | IRQV4       | 0x30068 | IRQ vector register4                | R/W | 0000h       |

|           | IRQV5       | 0x3006A | IRQ vector register5                | R/W | 0000h       |

|           | IRQV6       | 0x3006C | IRQ vector register6                | R/W | 0000h       |

|           | IRQV7       | 0x3006E | IRQ vector register7                | R/W | 0000h       |

|           | IRQV8       | 0x30070 | IRQ vector register8                | R/W | 0000h       |

|           | IRQV9       | 0x30072 | IRQ vector register9                | R/W | 0000h       |

|           | IRQV10      | 0x30074 | IRQ vector register10               | R/W | 0000h       |

|           | IRQV11      | 0x30076 | IRQ vector register11               | R/W | 0000h       |

|           | IRQV12      | 0x30078 | IRQ vector register12               | R/W | 0000h       |

|           | IRQV13      | 0x3007A | IRQ vector register13               | R/W | 0000h       |

|           | IRQV14      | 0x3007C | IRQ vector register14               | R/W | 0000h       |

|           | IRQV15      | 0x3007E | IRQ vector register15               | R/W | 0000h       |

Table 5-1. Special Registers (Continued)

NOTE: TSTC is used for factory test only. TSTC must not be accessed by program.

| Group     | Registers | Offset  | Description                         | R/W | Reset Value |

|-----------|-----------|---------|-------------------------------------|-----|-------------|

| Interrupt | FIQV0     | 0x30080 | FIQ vector register0                | R/W | 0000h       |

|           | FIQV1     | 0x30082 | FIQ vector register1                | R/W | 0000h       |

|           | FIQV2     | 0x30084 | FIQ vector register2                | R/W | 0000h       |

|           | FIQV3     | 0x30086 | FIQ vector register3                | R/W | 0000h       |

|           | FIQV4     | 0x30088 | FIQ vector register4                | R/W | 0000h       |

|           | FIQV5     | 0x3008A | FIQ vector register5                | R/W | 0000h       |

|           | FIQV6     | 0x3008C | FIQ vector register6                | R/W | 0000h       |

|           | FIQV7     | 0x3008E | FIQ vector register7                | R/W | 0000h       |

|           | FIQV8     | 0x30090 | FIQ vector register8                | R/W | 0000h       |

|           | FIQV9     | 0x30092 | FIQ vector register9                | R/W | 0000h       |

|           | FIQV10    | 0x30094 | FIQ vector register10               | R/W | 0000h       |

|           | FIQV11    | 0x30096 | FIQ vector register11               | R/W | 0000h       |

|           | FIQV12    | 0x30098 | FIQ vector register12               | R/W | 0000h       |

|           | FIQV13    | 0x3009A | FIQ vector register13               | R/W | 0000h       |

|           | FIQV14    | 0x3009C | FIQ vector register14               | R/W | 0000h       |

|           | FIQV15    | 0x3009E | FIQ vector register15               | R/W | 0000h       |

|           |           | Locati  | on 0x300A0 - 0x300A7 are not mapped |     |             |

| Interrupt | IRQSR     | 0x300A8 | IRQ shadow register                 | R   | xxxxxxxh    |

|           | FIQSR     | 0x300AC | FIQ shadow register                 | R   | xxxxxxxh    |

#### Table 5-1. Special Registers (Continued)

#### **ADCON** - A/D CONVERSION MODE REGISTER 0x3003C **Bit Identifier** .10 .15 .14 .13 .12 .11 .9 .8 .7 .5 .4 .3 .2 .6 .1 .0 **RESET Value** 0 0 \_ 0 0 0 0 0 0 0 0 \_ \_ \_ \_ \_ **Read/Write** R/W R/W R/W R/W R/W R R R R \_ [3:0] A/D conversion Data (Read-only) [4] Flash ADC Mode Selection 0 = Flash ADC0 mode 1 = Flash ADC1-4 mode [6:5] A/D Conversion Selection 00 =Select ADC1 01 = Select ADC2 10 = Select ADC3 11 = Select ADC4 [7] A/D Conversion Control Bit 0 = Stop A/D conversion1 = Start A/D conversion [9:8] A/D Conversion Time Selection $00 = f_{CPU}/4$ $01 = f_{CPU}/8$ $10 = f_{CPU}/16$ $11 = f_{CPU}/32$ [15:10] Not Used

### **BTCON** - BASIC TIMER CONTROL REGISTER

| Bit Identifier | .15   | .14                             | .13    | .12    | .11    | .10   | .9    | .8  | .7 | .6 | .5 | .4 | .3  | .2  | .1  | .0  |

|----------------|-------|---------------------------------|--------|--------|--------|-------|-------|-----|----|----|----|----|-----|-----|-----|-----|

| RESET Value    | 0     | 0                               | 0      | 0      | 0      | 0     | 0     | 0   | _  | _  | _  | _  | 0   | 0   | 0   | 0   |

| Read/Write     | R/W   | R/W                             | R/W    | R/W    | R/W    | R/W   | R/W   | R/W | _  | _  | _  | _  | R/W | R/W | R/W | R/W |

|                |       |                                 |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | [0] W | atcho                           | dog C  | ounte  | r (WT  | CNT)  | Clear | Bit |    |    |    |    |     |     |     |     |

|                |       | lo effe                         |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | 1 = V | Vatcho                          | dog co | unter  | clear  |       |       |     |    |    |    |    |     |     |     |     |

|                | [4] D | acie (                          | 201104 | or (D1 |        | Clear | D:4   |     |    |    |    |    |     |     |     |     |

|                |       | lo effe                         | Count  | er (Di | CNT)   | Clear | DI    |     |    |    |    |    |     |     |     |     |

|                |       |                                 | counte | r clea | r      |       |       |     |    |    |    |    |     |     |     |     |

|                | . – 6 |                                 | Journe |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | [3:2] | Cloc                            | k Sou  | rce Se | elect  |       |       |     |    |    |    |    |     |     |     |     |

|                |       | $X_{IN}/2^2$                    |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                |       | X <sub>IN</sub> /2 <sup>3</sup> |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                |       | $X_{IN}/2^2$                    |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | 11 =  |                                 |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                |       | ' IN                            |        |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | [7:4] | No E                            | ffect  |        |        |       |       |     |    |    |    |    |     |     |     |     |

|                | [15:8 | 8] Wat                          | chdog  | g Tim  | er Ena | able  |       |     |    |    |    |    |     |     |     |     |

|                | -     | -                               | = Disa | -      |        |       |       |     |    |    |    |    |     |     |     |     |

|                | Othe  | rs = E                          | nable  |        |        |       |       |     |    |    |    |    |     |     |     |     |

#### **BTCNT** - BASIC TIMER COUNTER REGISTER 0x30002 **Bit Identifier** .15 .14 .13 .12 .11 .10 .9 .8 .7 .6 .5 .4 .3 .2 .1 .0 **RESET Value** \_ 0 0 0 0 0 0 0 \_ \_ \_ \_ \_ \_ 0 \_ **Read/Write** \_ R R R R R R R R \_ \_ \_ \_ \_ [7:0] Basic Timer Counter Value (8 bit) [15:8] No Effect

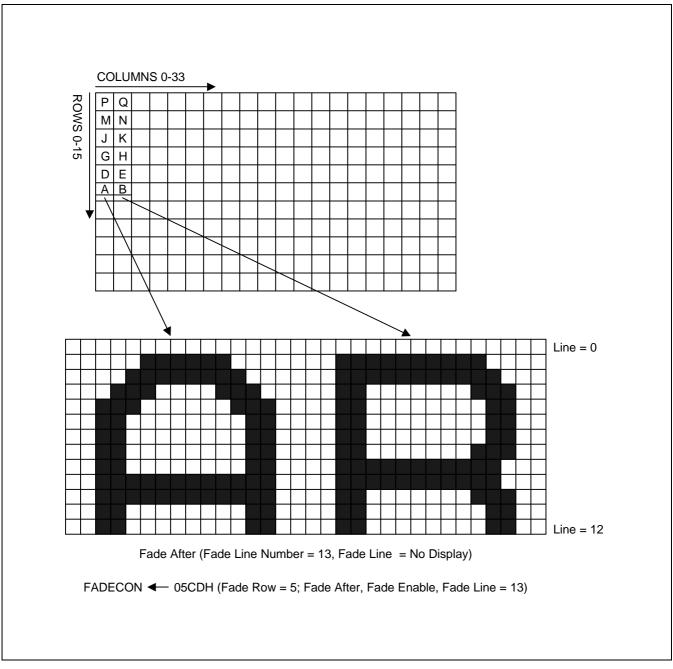

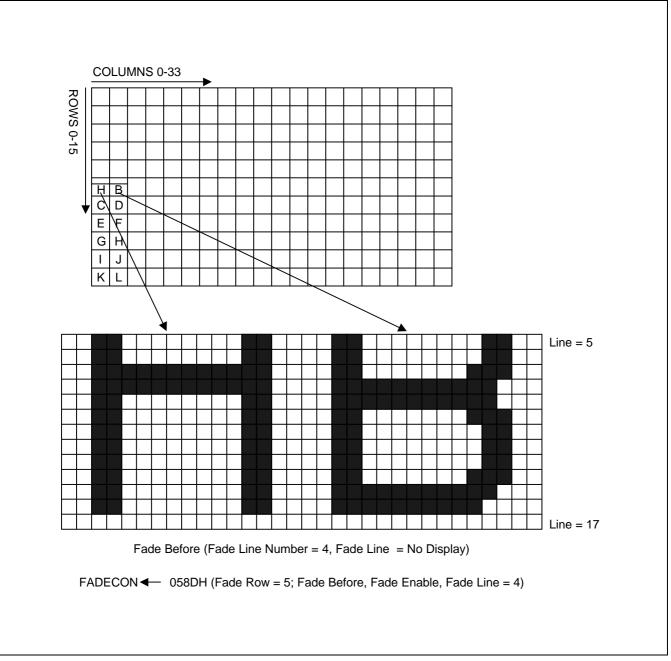

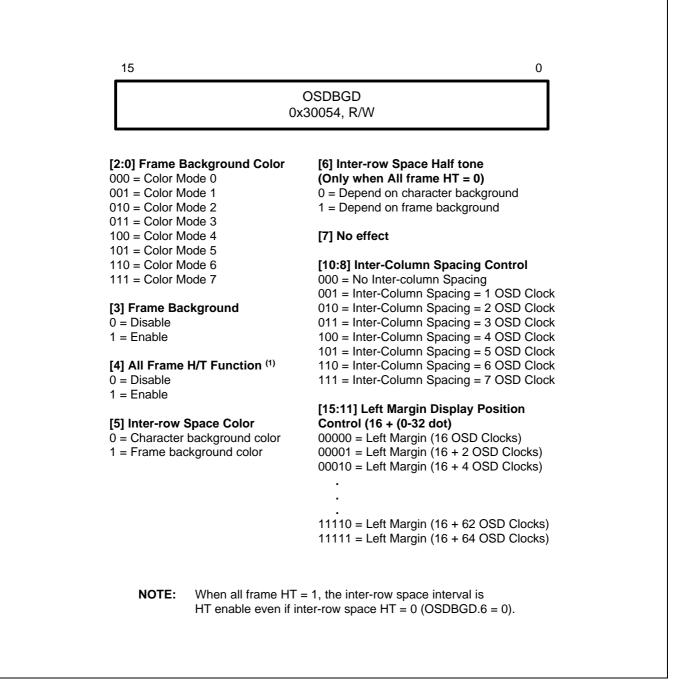

### FADECON - OSD FADE CONTROL REGISTER

| Dit Islamtifian | 45    |                    | 40      | 40    | 44       | 40       | •   | •   | -      | •              | -       |        | 2      | •      | 4   | •   |

|-----------------|-------|--------------------|---------|-------|----------|----------|-----|-----|--------|----------------|---------|--------|--------|--------|-----|-----|

| Bit Identifier  | .15   | .14                | .13     | .12   | .11      | .10      | .9  | .8  | .7     | .6             | .5      | .4     | .3     | .2     | .1  | .0  |

| RESET Value     | -     | -                  | -       | -     | 0        | 0        | 0   | 0   | 0      | 0              | 0       | 0      | 0      | 0      | 0   | 0   |

| Read/Write      | -     | -                  | -       | -     | R/W      | R/W      | R/W | R/W | R/W    | R/W            | R/W     | R/W    | R/W    | R/W    | R/W | R/W |

|                 |       |                    |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 | [5:0] | Fade               | Line    | Addre | ess (0-  | -17h)    |     |     | [6] Fa | ade Di         | irectio | on Sel | ectior | n Bit  |     |     |

|                 |       | er RO              |         |       | -        | ,        |     |     |        |                |         | matrix |        |        |     |     |

|                 |       | 000 = 1            |         |       | ,        |          |     |     |        | ade at         |         |        |        |        |     |     |

|                 |       | 01 = L             |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 | 0000  | )10 = L            | _ine 2  |       |          |          |     |     | [7] Fa | ade Fu         | unctio  | n Ena  | able B | it     |     |     |

|                 | 0000  | )11 = L            | _ine 3  |       |          |          |     |     | 0 = F  | ade di         | sable   |        |        |        |     |     |

|                 | 0001  | 00 = 1             | _ine 4  |       |          |          |     |     | 1 = F  | ade ei         | nable   |        |        |        |     |     |

|                 |       | 01 = L             |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 |       | 10 = L             |         |       |          |          |     |     |        |                |         | Addr   | ess S  | electi | on  |     |

|                 |       | 11 = L             |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 000 = 1            |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 001 = L            |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 10 = L             |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 11 = L             |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 00 = L             |         |       |          |          |     |     |        | = Rov          | -       |        |        |        |     |     |

|                 |       | 01 = L             |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 10 = L             |         |       |          |          |     |     | -      | = Rov          |         |        |        |        |     |     |

|                 |       | 11 = L             |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 1 = 000            |         |       |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 001 = 1            |         |       | noo lina | <u> </u> |     |     |        | = Rov<br>= Rov |         |        |        |        |     |     |

|                 |       | )10 = l<br>)11 = l |         | -     |          |          |     |     |        | = Rov<br>= Rov |         |        |        |        |     |     |

|                 |       | 00 = 1             |         | -     |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 00 = 1<br>01 = 1   |         | -     |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 10 = 1             |         | -     |          |          |     |     |        | = Rov          |         |        |        |        |     |     |

|                 |       | 11 = 1             |         | -     |          |          |     |     |        | - 1.01         | . 10    |        |        |        |     |     |

|                 |       | 000 = 1            |         |       |          |          |     |     | [15:1  | 2] No          | Effec   | t      |        |        |     |     |

|                 |       | )01 = I            |         | •     |          |          |     |     | •      | •              |         |        |        |        |     |     |

|                 |       | )10 = I            |         | -     |          |          |     |     |        |                |         |        |        |        |     |     |

|                 |       | )11 = I            |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 | 0111  | 00 = 1             | nter ro | w spa | ice line | e 11     |     |     |        |                |         |        |        |        |     |     |

|                 | 0111  | 01 = I             | nter ro | w spa | ice line | e 12     |     |     |        |                |         |        |        |        |     |     |

|                 |       | 10 = I             |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 |       | 11 = I             |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 |       | 000 = 1            |         |       | ice line | e 15     |     |     |        |                |         |        |        |        |     |     |

|                 |       | 01 = 1             |         |       |          |          |     |     |        |                |         |        |        |        |     |     |

|                 | 1111  | 11 = 1             | Not us  | ed    |          |          |     |     |        |                |         |        |        |        |     |     |

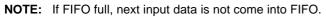

0x3001A

## **FIFOD** - FIFO DATA REGISTER

| Bit Identifier     | .15   | .14  | .13  | .12    | .11  | .10     | .9  | .8 | .7 | .6 | .5 | .4 | .3 | .2 | .1 | .0 |

|--------------------|-------|------|------|--------|------|---------|-----|----|----|----|----|----|----|----|----|----|

| <b>RESET Value</b> | -     | -    | -    | -      | -    | -       | -   | _  | x  | x  | x  | x  | x  | x  | x  | x  |

| Read/Write         | -     | -    | -    | -      | -    | _       | -   | -  | R  | R  | R  | R  | R  | R  | R  | R  |

|                    |       |      |      |        |      |         |     |    |    |    |    |    |    |    |    |    |

|                    | [7:0] | FIFO | Data | (8-Bit | Cour | nt Valu | ie) |    |    |    |    |    |    |    |    |    |

[15:8] No Effect

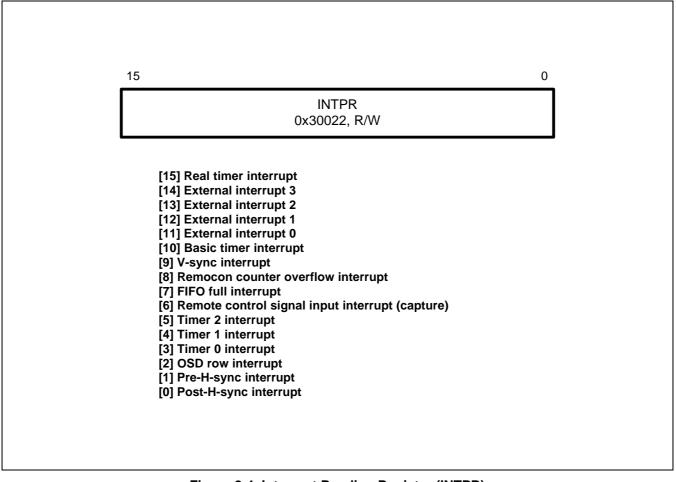

## **INTPR** - INTERRUPT PENDING REGISTER

| Bit Identifier     | .15   | .14    | .13      | .12     | .11    | .10    | .9      | .8     | .7     | .6  | .5  | .4  | .3  | .2  | .1  | .0  |

|--------------------|-------|--------|----------|---------|--------|--------|---------|--------|--------|-----|-----|-----|-----|-----|-----|-----|

| <b>RESET Value</b> | 0     | 0      | 0        | 0       | 0      | 0      | 0       | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write         | R/W   | R/W    | R/W      | R/W     | R/W    | R/W    | R/W     | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|                    |       |        |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

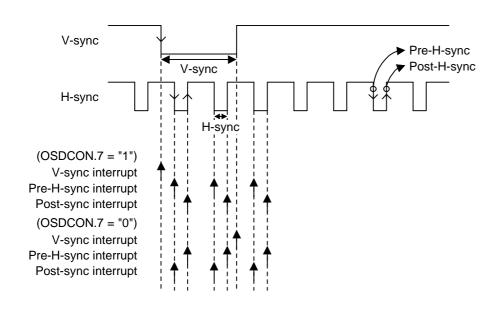

|                    | [0] 2 | nd ed  | no H-    | svnc i  | ntorri | Int    |         |        |        |     |     |     |     |     |     |     |

|                    |       | st edg | -        | -       |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | SD ro  |          | -       |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | imer ( |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | imer 1 |          | -       |        |        |         |        |        |     |     |     |     |     |     |     |

|                    | [5] T | imer 2 | 2 inter  | rupt    |        |        |         |        |        |     |     |     |     |     |     |     |

|                    | [6] R | emote  | e cont   | trol si | gnal i | nput i | interru | upt (C | apture | e)  |     |     |     |     |     |     |

|                    | [7] F | IFO fu | Ill inte | errupt  |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       |        |          |         | overf  | low ir | nterru  | pt     |        |     |     |     |     |     |     |     |

|                    |       | -sync  |          | -       |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | Basic  |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | Extern |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | Extern |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | Extern |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    |       | Extern |          |         |        |        |         |        |        |     |     |     |     |     |     |     |

|                    | [15]  | Real t | imer i   | nterru  | ipt    |        |         |        |        |     |     |     |     |     |     |     |

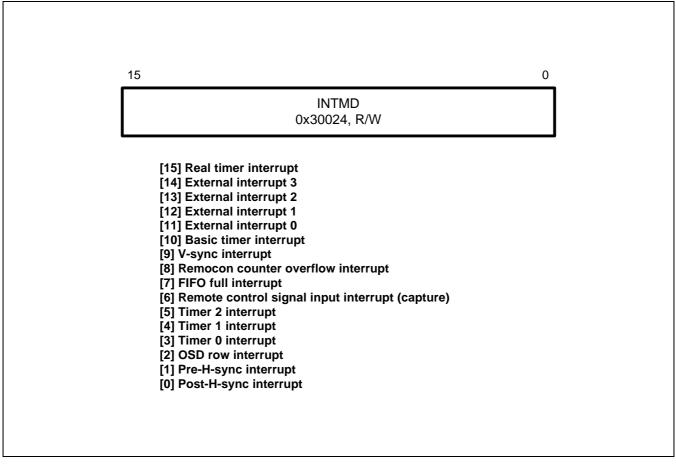

0x30024

# **INTMD** - INTERRUPT MODE REGISTER

| Bit Identifier     | .15   | .14    | .13     | .12    | .11     | .10     | .9      | .8     | .7    | .6  | .5  | .4  | .3  | .2  | .1  | .0  |

|--------------------|-------|--------|---------|--------|---------|---------|---------|--------|-------|-----|-----|-----|-----|-----|-----|-----|

| <b>RESET Value</b> | 0     | 0      | 0       | 0      | 0       | 0       | 0       | 0      | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write         | R/W   | R/W    | R/W     | R/W    | R/W     | R/W     | R/W     | R/W    | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|                    |       |        |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    | [0] 2 | nd ed  | ge H-   | sync i | interru | upt     |         |        |       |     |     |     |     |     |     |     |

|                    |       | st edg | -       | •      |         | -       |         |        |       |     |     |     |     |     |     |     |

|                    | [2] C | SD ro  | w int   | errup  | t       |         |         |        |       |     |     |     |     |     |     |     |

|                    | [3] T | imer ( | ) inter | rupt   |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | imer 1 |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | imer 2 |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       |        |         |        | -       | nput    | interru | upt (C | aptur | e)  |     |     |     |     |     |     |

|                    |       | IFO fu |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | emoc   |         |        | over    | flow ii | nterru  | pt     |       |     |     |     |     |     |     |     |

|                    |       | -sync  |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | Basic  |         |        | •       |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | Exteri |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | Exteri |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | Exteri |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    |       | Exteri |         |        |         |         |         |        |       |     |     |     |     |     |     |     |

|                    | [15]  | Roal t | imor i  | ntorri | int     |         |         |        |       |     |     |     |     |     |     |     |

[15] Real timer interrupt

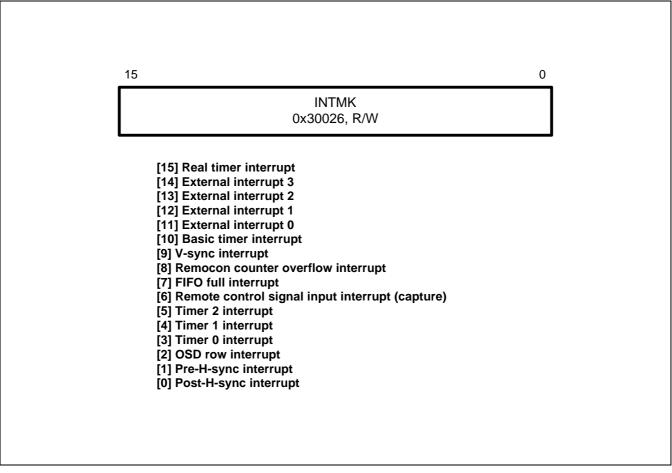

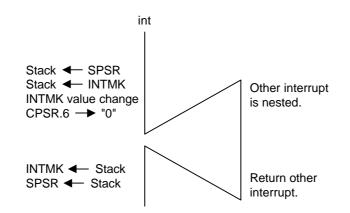

## **INTMK** - INTERRUPT MASK REGISTER

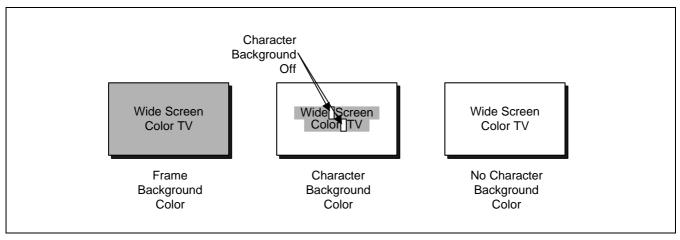

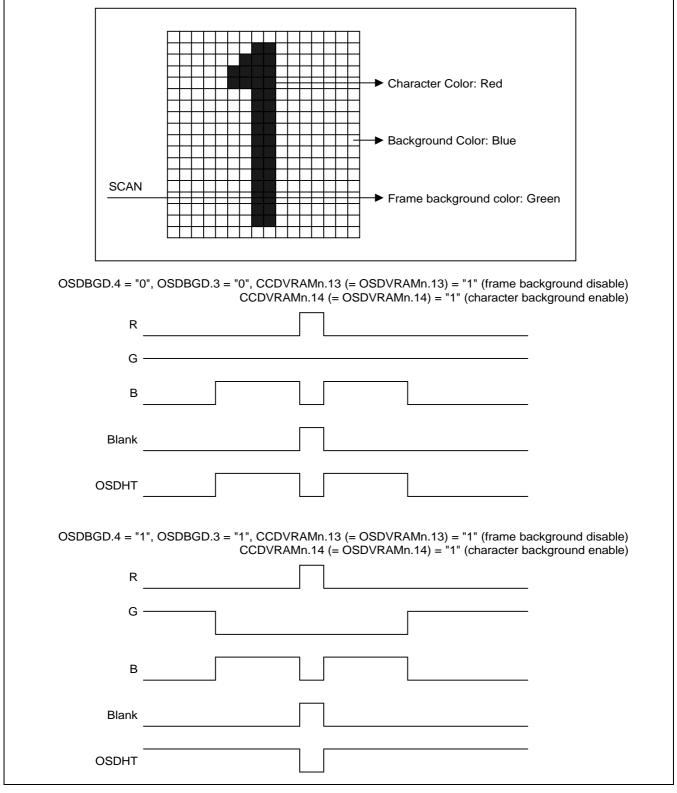

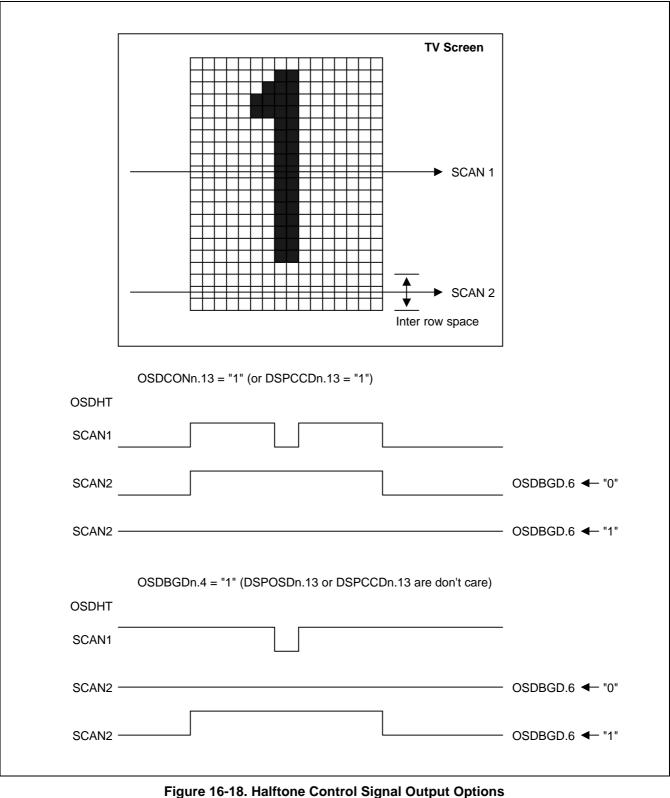

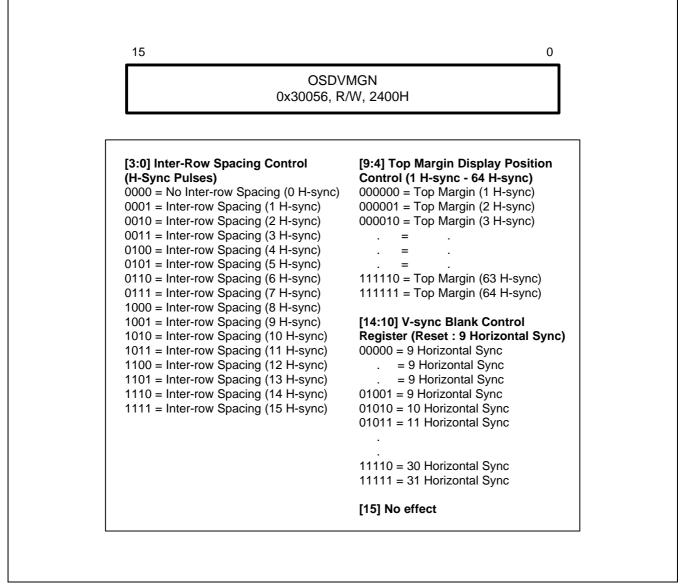

| Bit Identifier     | .15                                                                                                                   | .14                                                                                                                      | .13                                                                                                                                  | .12                                            | .11                                                          | .10               | .9  | .8  | .7     | .6  | .5  | .4  | .3  | .2  | .1  | .0  |